96-channel, Low Level Multiplexer

# INSTRUCTION MANUAL

February 26, 2001

(C) 1996, 1998, 2001 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

Model V243-S001

96-channel, Low-level Signal Conditioner

August 21, 1997

© 1997 Copyright by KineticSystems Corporation Lockport, Illinois All rights reserved

Page 1S of 2S

Model V243-S001

The Model V243-S001 is the same as the V243-VA41 except it has been modified to have filter settings to  $2~\rm{Hz},~10~\rm{Hz},~and~50~\rm{Hz}.$

August 21, 1997

# ${\bf ***Special\ Option ***}$

Model V243-S002

96-channel, Low-level Signal Conditioner

March 31, 2000

© 1997, 2000 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

Page 1S of 2S  $\,$

# Model V243-S002

The Model V243-S002 is the same as the V243-VA91 except it has been modified as follows:

Added front panel connectors (BNC/LEMO/SMB) to bring a differential voltage from an external calibration source into the module.

March 31, 2000

Model~V243-S003

96-channel, Low-level Signal Conditioner

June 26, 2000

© 1997, 2000 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

Page 1S of 2S

# Model V243-S003

The Model V243-S003 is the same as the V243-VA91 except that the filter cutoffs are 2Hz,  $10\rm Hz$  and  $50\rm Hz$  rather than  $10\rm Hz$ ,  $50\rm Hz$  and  $500\rm Hz$ .

June 26, 2000

# CONTENTS

| FEATURES AND APPLICATIONS         |    |

|-----------------------------------|----|

| GENERAL DESCRIPTION               |    |

| SIMPLIFIED BLOCK DIAGRAM          | 1  |

| Specifications                    |    |

| Ordering Information              | 3  |

| UNPACKING AND INSTALLATION        | 4  |

| Configuration                     | 4  |

| Module Insertion                  | 5  |

| FRONT PANEL DESCRIPTION           | 6  |

| LEDs                              |    |

| Connectors                        |    |

| V750-Isothermal Terminal Assembly |    |

| PROGRAMMING INFORMATION           | 8  |

| VXIbus Addressing                 |    |

| Channel Setup                     |    |

| Isothermal Channels               |    |

| Open Thermocouple Detection       |    |

| MUX-bus                           |    |

| Scan RAM                          |    |

| MUX-bus Rules                     |    |

| Overlap Detect Checklist          |    |

| Module Calibration                |    |

| Channel Calibration               |    |

| Suggestions for Highest Accuracy  | 23 |

| V243 Configuration Registers      | 24 |

| ID / Logical Address Register     |    |

| Device Type Register              |    |

| Status/Control Register           |    |

| Offset Register                   |    |

| Attribute Register                |    |

| Serial Number High                |    |

| Serial Number Low                 |    |

| Version Number Register           |    |

| Reserved                          |    |

| Interrupt Status Register         |    |

| Interrupt Control Register        |    |

| Subclass Register                 |    |

| Suffix High Register              |    |

| Suffix Low Register               |    |

| User Defined Registers            |    |

| Oser Defined Registers            |    |

| V243 OPERATIONAL REGISTERS                                                 | 32 |

|----------------------------------------------------------------------------|----|

| Configuration Register                                                     |    |

| Calibration Register                                                       |    |

| Output Buffer Register                                                     | 33 |

| Prefilter Gain Registers                                                   |    |

| Postfilter Gain Registers                                                  |    |

| Scan Ram                                                                   | 36 |

| Correction Table                                                           | 37 |

| APPENDIX                                                                   | 42 |

| APPENDIX A - DRIVING BALANCED ANALOG INPUTS FROM UNBALANCED SOURCES        | A1 |

| APPENDIX B - C/C++ PROGRAMMING EXAMPLES USING NATIONAL INSTRUMENTS DRIVERS | B1 |

| APPENDIX C - ADDITIONAL SPECIFICATIONS.                                    | C1 |

| APPENDIX D - REGISTER LAYOUT FOR CONFIGURATION AND OPERATIONAL REGISTERS   | D1 |

| FIGURES                                                                    |    |

| FIGURE 1 - V243 SWITCH LOCATIONS                                           | 4  |

| FIGURE 2 - V750- ZB11                                                      |    |

| FIGURE 3 - CHANNEL SETUP                                                   | 10 |

| FIGURE 4 - 68 PIN SCSI II CONNECTORS: P3, P4, P5, AND P6                   | 38 |

| TABLES                                                                     |    |

| TABLE 1 - SCAN RAM / SCAN TABLE EXAMPLE                                    | 13 |

| TABLE 2 - V243 SCAN TABLE, MUX-BUS PATH.                                   | 17 |

| TABLE 3 - CALIBRATION REGISTER VALUES                                      |    |

| TABLE 4 - 68 PIN SCSI II CONNECTORS: P3, P4, P5, AND P6 PINOUT             | 39 |

| Warranty                                                                   |    |

| vv arramby                                                                 |    |

Warranty DWP

# 96-channel, Low-level Signal Conditioner

# Provides exceptionally high accuracy at low input levels

V243

#### **Features**

- Use with V208 host ADC

- 16, 32, 48, 64 or 96-channel input options

- Differential inputs and programmable gain per channel

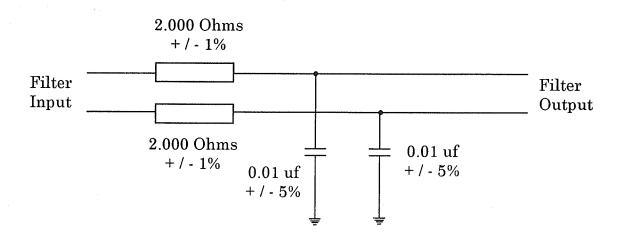

- 2-pole, active Butterworth, low-pass filters with programmable cutoff: 10, 50, 500 Hz, or 5 kHz bypass

- Open-thermocouple detection option available

- End-to-end channel calibration

# **Typical Applications**

- Automotive body engineering tests

- · Automotive powertrain testing

- · Automotive safety tests

- · Aircraft engine testing

- Rocket engine testing

- · Satellite testing

# General Description (Product specifications and descriptions subject to change without notice.)

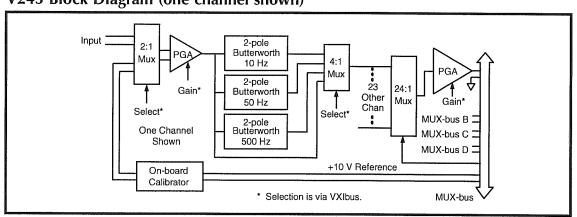

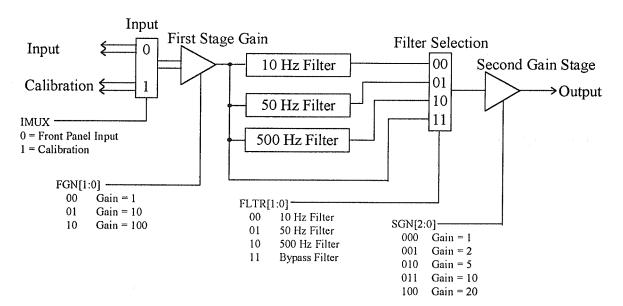

The Model V243 is a single-width, C-size, register-based, VXIbus module that is designed for thermocouple and other low-bandwidth, low-level signal applications. It provides up to 96 differential-input channels with programmable gain per channel and 2-pole, active, low-pass Butterworth filters on each channel. Filter cutoff frequencies of 10, 50 and 500 Hz plus bypass are software-selectable. Software-selectable pre-filter gains of 1, 10, and 100 are provided for each channel. Both filter cutoff and pre-filter gains are programmable in groups of eight channels. A common, multiplexed, post-filter gain of 1, 2, 5, 10, or 20 is selectable on a channel by channel basis. This allows a programmable gain per channel from 1 to 2000 ( $\pm$ 10 V to  $\pm$ 5 mV full scale range).

The V243 is designed to work with the V208 16-bit, 100,000 Sample/second ADC module which supports up to 2048 input channels using MUX-bus<sup>TM</sup>. Up to 11 V243s can be placed in adjacent slots to the right of the V208 to provide a full 1056 active input channels.

From one to eleven V243s combined with the V208 provide a low-noise analog subsystem with built-in, per-channel calibration that is traceable to NIST standards. The V208 includes a precision reference source that is calibrated at the factory, and each V243 includes a precision calibrator. Each input channel can be connected to the calibrator output, ground, or the analog input under software control. In addition, for maximum accuracy, a small correction factor for each calibrator output is stored in a EEPROM within each V243. This correction factor can be applied during the calibration process to obtain maximum accuracy.

The V243 supports both static and dynamic configuration. It may be accessed using A24/A16, D16 data

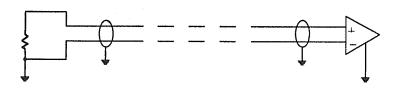

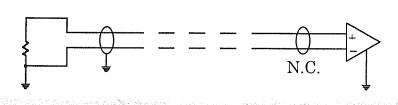

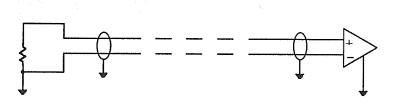

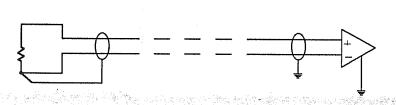

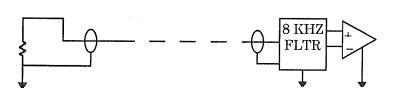

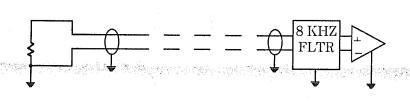

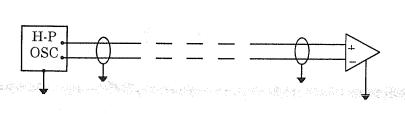

# V243 Block Diagram (one channel shown)

| Item                                | S                                                 | pecification                     |

|-------------------------------------|---------------------------------------------------|----------------------------------|

| General                             |                                                   |                                  |

| Number of channels                  | 16, 32, 48, 64 or 96, differentia                 | l input                          |

| Gain ranges                         | 1, 2, 5, 10, 20, 50, 100, 200, 50                 | 00, 1000, 2000                   |

| Cutoff frequencies                  | 10 Hz, 50 Hz, 500 Hz, and Byp                     |                                  |

| Input                               |                                                   |                                  |

| Input range                         |                                                   |                                  |

| Common mode:                        | ±10.24 V                                          |                                  |

| Differential:                       | ±10.24 V                                          |                                  |

| Input protection                    | ±35 V continuous                                  |                                  |

| Input impedance                     |                                                   |                                  |

| ZAxx Options:                       | >100 MΩ                                           |                                  |

| VAxx Options:                       | 10 ΜΩ                                             |                                  |

| Input impedance (Over temperature ) |                                                   |                                  |

| ZAxx Options:                       | 20 MΩ min; 100 MΩ typical                         |                                  |

| VAxx Options                        | 10 ΜΩ                                             |                                  |

| Transfer Characteristics            |                                                   |                                  |

| Linearity error                     | ±0.0015% FSR                                      |                                  |

| Initial accuracy, RTI*              | After automatic calibration usin                  | g a V208:                        |

|                                     | ZAxx Options                                      | VAxx Options                     |

| Gain = 1                            | ±(900 μV + 0.01% of reading)                      | ·                                |

| Gain = 10                           | ±(90 µV + 0.01% of reading)                       | $\pm$ (90 µV + 0.04% of reading) |

| Gain = 100                          | $\pm (9 \mu\text{V} + 0.01\% \text{ of reading})$ | ±(9 μV + 0.04% of reading)       |

| Gain = 2000                         | $\pm (2  \mu V + 0.04\% \text{ of reading})$      | ±(2 μV + 0.04% of reading)       |

| Offset stability, RTI               | 0.5 μV/°C @ gain ≥ 1000                           | ( ]                              |

| Gain stability                      | 15 ppm/°C                                         |                                  |

| Bandwidth                           | 5 kHz                                             |                                  |

| Common mode rejection               | -120 dB typical, -110 dB min at                   | gain ≥ 100                       |

| Noise, RTI                          | 1 μV RMS typical, gain ≥ 1000                     | _                                |

| Channel-to-channel crosstalk, RTI   |                                                   |                                  |

| Gain = 1 to Gain = 1                | 90 dB                                             |                                  |

| Gain = 1 to Gain = 2000             | 135 dB                                            |                                  |

| I/O Connector Type                  | 68P High Density (24 channels                     | per connector)                   |

| Power Requirements (quiescent)      | ±5V +24V                                          | -24V                             |

| V243-VA11                           | 1.8 A 220 mA                                      | 190 mA                           |

| V243-VA31                           | 1.8 A 360 mA                                      | 300 mA                           |

| V243-VA41, V243 -ZA11               | 1.8 A 460 mA                                      | 370 mA                           |

| V243-VA61                           | 2.0 A 650 mA                                      | 520 mA                           |

| V243-VA91, V243-ZA21                | 2.0 A 850 mA                                      | 670 mA                           |

| Environmental and Mechanical        |                                                   |                                  |

| Temperature range                   |                                                   |                                  |

| Operational                         | 0°C to + 50°C                                     |                                  |

| Storage                             | -25°C to + 75°C                                   |                                  |

| Relative humidity                   | 0 to 85%, non-condensing to 40                    | o°C                              |

| Cooling requirements                | 10 CFM                                            |                                  |

| Dimensions                          | 340 mm x 233.35 mm x 30.48 r                      | nm (C-size VXIbus)               |

| Front-panel potential               | Chassis ground                                    | ,                                |

| * Includes V208 quantization error. | 1                                                 |                                  |

<sup>\*</sup> Includes V208 quantization error.

# V243 (continued)

# **Ordering Information**

Model V243-ZA11 48-channel, Low-level Multiplexer

Model V243-ZA21 96-channel, Low-level Multiplexer

Model V243-VA11 16-channel, Low-level Multiplexer with Open Thermocouple Detection

Model V243-VA31 32-channel, Low-level Multiplexer with Open Thermocouple Detection

Model V243-VA41 48-channel, Low-level Multiplexer with Open Thermocouple Detection

Model V243-VA61 64-channel, Low-level Multiplexer with Open Thermocouple Detection

Model V243-VA91 96-channel, Low-level Multiplexer with Open Thermocouple Detection

Please note: The V208 must be used as the host ADC for the V243 (not the V207).

**Related Products**

| Model V208      | 16-bit, 100,000 Sample/second ADC Subsystem     |

|-----------------|-------------------------------------------------|

| Model 5868-Bxyz | Cable—68S High Density to Unterminated          |

| Model 5868-Dxyz | Cable—68S High Density to 68P High Density      |

| Model V750-ZB11 | Termination Assembly for 48 Channel (V243-VA41) |

| Model V765-ZA11 | Rack-mount Termination Panel                    |

| Model V765-ZB11 | Rack-mount Termination Panel with Improved CMR  |

| Model V792-ZA11 | Rack-mount Isothermal Termination Panel         |

Model V792-ZB11 Rack-mount Isothermal Termination Panel with Improved CMR

# Unpacking and Installation

At KineticSystems, static precautions are observed from production, test, and packaging of the module. This includes using static proof mats and wrist straps. Please observe these same precautions when unpacking and installing the module whenever possible.

The Model V243 is shipped in an anti-static bag within a styrofoam packing container. Carefully remove the module from its static-proof bag and prepare to set the logical address switches to the appropriate value.

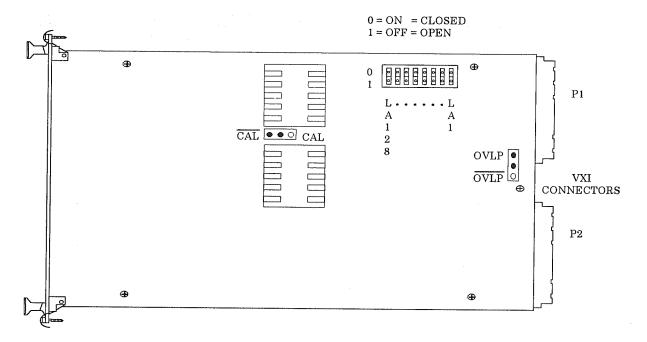

FIGURE 1 - V243 Switch Locations

## Configuration

There is one set of user configurable switches on the V243. All eight switches, #1 (MSB) to #8 (LSB), are for the logical address. The logical address may be set from 1 to 254 as a statically configured device. If the module is set for logical address 255 (all switches open), then the V243 will be dynamically configured by the resource manager. A logical address of 0 is not valid since it is reserved for the Slot 0 controller. Logical address 255 is the factory default setting.

A three position strap is located between two heatsinks. This strap is used to enable write access to a correction table used during the module (factory) calibration. The V243 can be recalibrated if this strap is moved to the enabled position (right). The factory default for the cal strap is to the disabled position to protect accidental erasure of the correction table.

There is also a three position strap located between the P1 and P2 connectors. A strap may be placed on the upper two strap posts to enable this modules overlap detect capability (factory default). When enabled on all of the signal conditioning modules, the V243 will be able to detect if multiple modules are attempting to output a voltage out on MUX-bus at the same time. An overlap may occur if a module is incorrectly programmed. More detail is provided on page 12 about overlap detect and how it relates to MUX-bus.

#### **Module Insertion**

The V243 is a C-sized, single width, VXIbus module. Except for Slot 0 or Slot 1, it can be mounted in any unoccupied slot in a C-size VXIbus mainframe. Since the V243 is a signal conditioning module that uses MUX-bus, this module must be plugged into the VXI mainframe to the right of the V208 or another signal conditioning module in order to use MUX-bus. MUX-bus is a proprietary local bus that the signal conditioning modules (like the V243) use to send voltages to the V208.

CAUTION: TURN MAINFRAME POWER OFF WHEN INSERTING OR REMOVING MODULE

WARNING: REMEMBER TO REMOVE INTERRUPT ACKNOWLEDGE DAISY-CHAIN JUMPERS PRIOR TO INSERTING THIS MODULE IN THE BACKPLANE OR USE AN AUTOCONFIGURING BACKPLANE

If the mainframe does not have an autoconfiguring backplane, special care is necessary when installing the V243. To insure proper interrupt acknowledge cycles from the V243 module, the daisy-chain Interrupt Acknowledge jumper must be removed before the module is installed in a slot. Conversely, daisy-chain jumpers must be installed in any empty slot between the V243 and the Slot 0 Controller.

# Front Panel Description

#### **LEDs**

The Add Rec (address received) LED lights to indicate the V243 is being accessed through VXI. The Overlap (overlap detect) LED will light to indicate that another module tried to output its voltage out on the MUX-bus at the same time the V243 did. If the overlap detect LED is on, the V243 will not output any voltages out on MUX-bus.

#### Connectors

The V243 has two or four 68 pin, high density SCSI type connectors depending on the option. Each connector has 24 differential inputs as well as a buffered output of the first channel on that connector, a calibration output used during module calibration, and an isothermal reference input. See Figure 4 and Table 4 (Pages 38 and 39) for the precise pinout descriptions. The on board, 10 volt reference can be calibrated by adjusting the voltage through the pot labeled Ref Adj (Reference Adjust) on the front panel. The "on board" reference-voltage can be monitored through the connectors labeled "+" and "-".

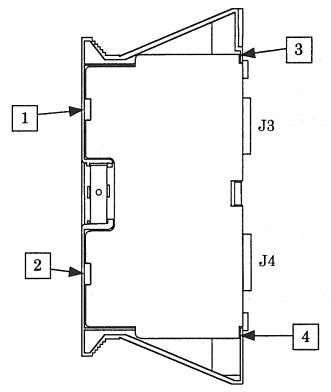

# V750-Isothermal Terminal Assembly

The V750-ZB11 is an isothermal termination assembly specifically designed for the V243. This assembly is capable terminating up to 48 channels. The isothermal reference is connected to the isothermal channel located on the J3 connector. This isothermal channel may be entered into the V243 scan list as channel 97. A detailed explanation on the use of this reference is on page 11.

In cases where the V243 is used in applications other than with thermocouples, the V750 can be used as a general purpose termination assembly. The reference is simply not used to measure the temperature of the assembly.

To remove the cover of the V750 pry at points 1 and 2 with a screwdriver until the bottom of the cover is clear of the front side of the termination assembly. The cover should easily lift off the assembly.

To put the cover back on, insert the pegs at points 3 and 4. Then push down at points 1 and 2 until the latches in front are hooked in the slots.

FIGURE 2 - V750- ZB11

# **Programming Information**

# **VXIbus Addressing**

The V243 is classified as an extended register device which means it has registers that occupy A16 and A24 space. In accordance with the VXI specification, A16 space means that only 16 address bits are decoded by the V243. A16 registers occupy the address space from 0 to 65535. A24 space means that 24 address bits are decoded by the V243. A24 registers occupy the address space from 0 to 16777215.

The configuration registers are located in A16 space and include the standard registers defined by VXI as well as additional, general purpose registers. From these registers, information about the specific module can be read, the base address for the A24 registers can be controlled, and the interrupt level can be set. For example, by reading certain registers in A16 space, the following information about this module can be found just by knowing the module's logical address:

Manufacturer:

KineticSystems

Module Type:

V243

Option:

ZA21 20

Serial Number:

1.0

Firmware Version:

1.0

Hardware Version:

1.0

In general, any configuration register can be accessed simply by knowing the module's logical address (set by the logical address switches) and the register's offset. A complete list of A16 register descriptions and their offsets is available starting at pages D-1 and 24.

$A16\_ADDRESS = C000_{16} + (LOGICAL\_ADDRESS \bullet 40_{16}) + A16\_REGISTER\_OFFSET$

Manufacturer: can be found by looking at bits 11 through 0 at register offset 0<sub>16</sub>. If the value is F29<sub>16</sub>, this indicates that the module was built by KineticSystems.

Module Type: can be found by looking at bits 11 through 0 at register offset 2<sub>16</sub>. If the value is a BCD (Binary Coded Decimal) number 243, this indicates that the module is a V243.

Option: can be found by reading the four character string located at registers at offsets  $20_{16}$  and  $22_{16}$ . If the strings "ZA" is found at offset  $20_{16}$  and "21" is found at offset  $22_{16}$ , then the specific type of module is the V243-ZA21 meaning the this module does not have open thermocouple detection and has 96 channels. The suffix registers are additional registers defined by KineticSystems to aid in identifying a module. It is not a standard register defined by the VXI spec.

Serial Number: can be found reading the 32-bit, unsigned number stored in registers at offsets  $A_{16}$  and  $C_{16}$ . For example, if a the serial number was 20, the values in the Serial

Number High Register would be 0<sub>16</sub> and the value in the Serial Number Low Register would be 14<sub>16</sub>.

Firmware Version: can be found by reading the BCD number stored in bits 15 through 8 of the Version Number Register at offset E<sub>16</sub>.

Hardware Version: can be found by reading the BCD number stored in bits 7 through 0 of the Version Number Register at offset E<sub>16</sub>.

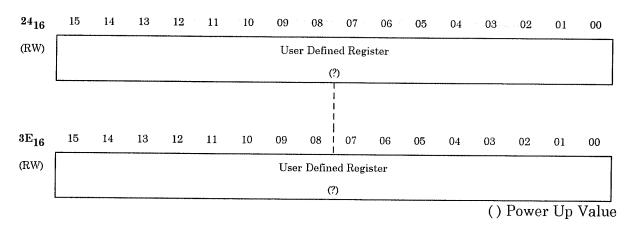

In addition to the Suffix Registers, KineticSystems has left registers at offsets 24<sub>16</sub> through 3E<sub>16</sub> open for user definition. These User Defined Registers can also be used to identify the module (i.e., with an internal identification number). These registers can only be written one at a time and only at 3 mS intervals, but once they have been written, the data is retained even after power has been removed.

The operational registers are located in A24 space and include the registers specific to V243 modules. This address space is configured by the resource manager. These registers include channel setup and calibration registers. In general, any operational register can be accessed simply by knowing the value in the modules Offset Register (Operational register in A24 space at offset 6).

$A24\_ADDRESS = (OFFSET\_REGISTER\_VALUE \bullet 100_{16}) + A24\_REGISTER\_OFFSET$

Prefilter Gain Registers (page 34) - Controllable in groups of eight channels.

| <br>15 | 14   | 13  | 12  | 11  | 10  | 09   | 08   | 07  | 06  | 05  | 04  | 03   | 02   | 01   | 00   |

|--------|------|-----|-----|-----|-----|------|------|-----|-----|-----|-----|------|------|------|------|

|        | IMUX |     |     |     |     | FLTR | FLTR |     |     |     | . r |      | 1    | FGN1 | FGN0 |

|        |      |     |     |     |     | 1    | 0    |     |     |     |     |      |      |      |      |

| (1)    | (0)  | (1) | (1) | (1) | (1) | (0)  | (0)  | (1) | (1) | (1) | (1) | (1)  | (1)  | (0)  | (0)  |

|        |      |     |     |     |     |      |      |     |     |     |     | () P | ower | Up V | alue |

Post Gain Registers (page 35) - Controllable on a per channels basis.

|   | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02           | 01           | 00            |    |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------|--------------|---------------|----|

|   | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (2) | (2) | (2) | (2) | (2) | l            |              | SGN0          |    |

| İ | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (?) | (?) | (?) | (?) | (?) | (?)<br>) Pow | (?)<br>er U1 | (?)<br>) Valu | ue |

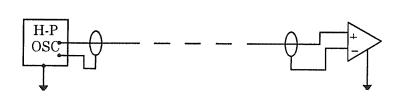

FIGURE 3 - Channel Setup

# Channel Setup

The V243 has two separate gain stages. The first gain stage is applied before the filter and is controllable in groups of eight channels. First stage gain can be changed by writing bits 1 and 0 of the Prefilter Gain Register. First stage gain may be set to 1, 10, or 100. The second stage gain is applied after the filter and is controllable on a per channel basis. Second stage gain is set by writing bits 2 to 0 of the Postfilter Gain Register. Second stage gain may be set to 1, 2, 5, 10, or 20.

In general, it is best to apply the most possible gain in the first stage. For example, a gain of 10 can be accomplished by applying the gain of 10 in the first or second stage. In this case, a gain of 10 should be applied in the first stage for best noise immunity.

During normal operation, the input of each channel can be selected to connect to the 68 pin, high density, SCSI II type connector by setting bit 14 of the Prefilter Gain Register to zero. Setting this bit to a one will set the channel to the calibration signal. During calibration, each channel can be selected to connect to the calibration voltage. The calibration voltage is set by writing to the Calibration Register (Operation register in A24 space at offset 2<sub>16</sub>).

#### **Isothermal Channels**

In addition to the analog input channels, the V243 can have up to four isothermal reference channels, one for each connector. When the V243 is connected to an isothermal panel or assembly, these reference channels will output voltage 100 mV/°C. These reference channels are considered channels 97 through 100 when setting up MUX-bus. Although these channels go through the same second stage gain (post-filter) and MUX-bus paths as the other channels, the reference must always have a gain of 1 and does not get calibrated along with the other channels. Since the second stage gain can be applied on a pre channel basis, setting the gain to one for the reference channel will not restrict the gain settings for any one channel.

# Open Thermocouple Detection

The V243-ZB11, V243 ZB21, and the V243-VAxx options have the capability to detect open thermocouples. The detection is enabled by setting bit 7 of the Configuration Register (Operational Register in A24 space offset, 0<sub>16</sub> page 32). Once enabled, any channel that is open will be set to positive full scale, but any other channel will remain in its normal range. Because current is injected into each channel while the open thermocouple detection is enabled, the channel's accuracy will be affected. Therefore, when detection is enabled, no channels may be calibrated nor can valid data be taken.

#### MUX-bus

The MUX-bus makes use of the VXI P2 LBUS (local bus) connector lines. Signal conditioning modules supporting the MUX-bus must be plugged into a slot to the right of the V208 or another signal conditioning module.

# The MUX-bus pin definition (P2) is:

LBUS00 MUX path A signal hi LBUS01 MUX path A signal lo LBUS02 MUX path B signal hi LBUS03 MUX path B signal lo LBUS04 MUX path C signal hi LBUS05 MUX path C signal lo LBUS06 MUX path D signal hi LBUS07 MUX path D signal lo LBUS08 Reference Hi LBUS09 Reference Lo LBUS10 Overlap Detect LBUS11 MUX-bus Clock

The MUX-bus clock generates the control signal that causes the output multiplexers on the signal conditioning modules to increment to the next channel.

Reference Hi and Reference Lo provide a +10 volt differential signal to adjacent signal conditioning modules, allowing all channels to be referenced to a common standard. The entire system can be calibrated to this reference under software control. This greatly simplifies system calibration.

Overlap Detect is used by the signal conditioning modules to detect if two or more modules are attempting to output their voltages at the same time. This helps prevent conflicts caused by an incorrectly programmed Scan RAM (Scan RAM is used to control MUX-bus). Should an overlap condition occur, the V243 will stop outputting any voltages out on MUX-bus.

#### Scan RAM

NOTE: As a general rule, the V208 or any other receiving MUX module, should be the FIRST to be put in "setup" mode and the LAST to be put in "run" mode.

Table 1 shows an example of how Scan RAM might be setup in a case using a V243, V252, and a V208. In the example, 16 channels of V243 are assigned to the first 16 channels of V208. Eight Channels of the V252 (16 channel filter module) is then assigned to the next eight channels on the V208 for a total of 24 channels.

TABLE 1 - Scan RAM / Scan Table Example

| Scan Table Pointer | V243 Scan Table Data             | V252 Scan Table Data             | V208 Scan Table Data             | Channel Enabled |

|--------------------|----------------------------------|----------------------------------|----------------------------------|-----------------|

| 2E <sub>16</sub>   | 1000 0000 0000 01112             | 1100 0000 0000 01117             | 1000 0000 0000 0111 <sub>2</sub> | V252 Channel 8  |

| 2C <sub>16</sub>   | 0000 0000 0000 01112             | 0100 0000 0000 01112             | 0000 0000 0000 01112             | V252 Channel 7  |

| 2A <sub>16</sub>   | 0000 0000 0000 01012             | 0100 0000 0000 01102             | 0000 0000 0000 01102             | V252 Channel 6  |

| 2816               | 0000 0000 0000 01012             | 0100 0000 0000 01012             | 0000 0000 0000 01012             | V252 Channel 5  |

| 2616               | 0000 0000 0000 01002             | 0100 0000 0000 01002             |                                  |                 |

| 1                  | i -                              | 1                                | 0000 0000 0000 00112             | V252 Channel 4  |

| 24 <sub>16</sub>   | 0000 0000 0000 00102             | 0100 0000 0000 00102             | 0000 0000 0000 00102             | V252 Channel 3  |

| 2216               | 0000 0000 0000 00012             | 0100 0000 0000 00012             | 0000 0000 0000 00012             | V252 Channel 2  |

| 2016               | 0000 0000 0000 0000 <sub>2</sub> | 0100 0000 0000 0000 <sub>2</sub> | 0000 0000 0000 0000 <sub>2</sub> | V252 Channel 1  |

| 1E <sub>16</sub>   | 0100 0000 0000 11112             | 0000 0000 0000 11112             | 0000 0000 0000 11112             | V243 Channel 16 |

| 1C <sub>16</sub>   | 0100 0000 0000 11102             | 0000 0000 0000 11102             | 0000 0000 0000 11102             | V243 Channel 15 |

| 1A <sub>16</sub>   | 0100 0000 0000 11012             | 0000 0000 0000 11012             | 0000 0000 0000 11012             | V243 Channel 14 |

| 18 <sub>16</sub>   | 0100 0000 0000 11002             | 0000 0000 0000 11002             | 0000 0000 0000 11002             | V243 Channel 13 |

| 1616               | 0100 0000 0000 10112             | 0000 0000 0000 10112             | 0000 0000 0000 10112             | V243 Channel 12 |

| 14 <sub>16</sub>   | 0100 0000 0000 1010 <sub>2</sub> | *0000 0000 0000 10102            | 0000 0000 0000 1010 <sub>2</sub> | V243 Channel 11 |

| 12 <sub>16</sub>   | 0100 0000 0000 10012             | 0000 0000 0000 10012             | 0000 0000 0000 10012             | V243 Channel 10 |

| 1016               | 0100 0000 0000 1000 <sub>2</sub> | 0000 0000 0000 10002             | 0000 0000 0000 1000 <sub>2</sub> | V243 Channel 9  |

| E <sub>16</sub>    | 0100 0000 0000 01112             | 0000 0000 0000 01112             | 0000 0000 0000 01112             | V243 Channel 8  |

| C <sub>16</sub>    | 0100 0000 0000 0110 <sub>2</sub> | 0000 0000 0000 0110 <sub>2</sub> | 0000 0000 0000 01102             | V243 Channel 7  |

| A <sub>16</sub>    | 0100 0000 0000 01012             | 0000 0000 0000 01012             | 0000 0000 0000 01012             | V243 Channel 6  |

| 8 <sub>16</sub>    | 0100 0000 0000 0100 <sub>2</sub> | 0000 0000 0000 0100 <sub>2</sub> | 0000 0000 0000 0100 <sub>2</sub> | V243 Channel 5  |

| 616                | 0100 0000 0000 00112             | 0000 0000 0000 00112             | 0000 0000 0000 00112             | V243 Channel 4  |

| 4 <sub>16</sub>    | 0100 0000 0000 0010 <sub>2</sub> | 0000 0000 0000 0010 <sub>2</sub> | 0000 0000 0000 0010 <sub>2</sub> | V243 Channel 3  |

| 2 <sub>16</sub>    | 0100 0000 0000 00012             | 0000 0000 0000 00012             | 0000 0000 0000 00012             | V243 Channel 2  |

| 016                | 0100 0000 0000 00002             | 0000 0000 0000 0000 <sub>2</sub> | 0000 0000 0000 0000 <sub>2</sub> | V243 Channel 1  |

Please Note: The Scan Tables for each MUX-bus module are identical except only one module has the enable bit set at any one time. If this rule is not observed, an overlap condition will occur because two modules will try to output voltages on MUX-bus at the same time.

V243 and V252 Scan RAM (starts at A24 offset 200<sub>16</sub>)

| 15  | 14    | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06 | 05 | 04   | 03     | 02   | 01 | 00 |

|-----|-------|-----|-----|-----|-----|-----|-----|-----|----|----|------|--------|------|----|----|

| EOL | Enabl |     |     |     |     |     |     |     |    |    | Chan | nel Nu | mber |    |    |

| (?) | (?)   | (?) | (?) | (?) | (?) | (?) | (?) | (?) |    |    |      |        |      |    |    |

() Power Up Value

# V208 Scan RAM (starts at A32 offset 1000<sub>16</sub>)

| 15         | 14           | 13  | 12  | 11  | 10 | 09 | 08 | 07 | 06   | 05      | 04    | 03 | 02 | 01 | 00 |

|------------|--------------|-----|-----|-----|----|----|----|----|------|---------|-------|----|----|----|----|

| EOL<br>(?) | Enabl<br>(?) | (?) | (?) | (?) |    |    |    |    | Chan | inel Nu | ımber |    |    |    |    |

() Power Up Value

# For this example:

MUX-bus on the V208 always scans at 200 kHz (5 µS convert time)

If there are 24 channels in the Scan Table and since the V208 is a scanning ADC, then the scan rate must be less than or equal to 200 kHz / 24 channels = 8333 Hz. The scan rate determines how often the MUX-bus modules run through the Scan Table.

Let scan rate = 8 kHz,  $t_{SCAN} = 1 / 8 \text{ kHz} = 125 \mu S$ .

# Every 125 µS:

1.) Scan Table Pointer is set to  $0_{16}$ .

V243 reads 4000<sub>16</sub>. Enable bit is set. Channel 1 is indicated.

V243 outputs its channel 1 voltage.

V252 reads 0000<sub>16</sub>. Enable bit is not set.

V252 waits.

$V208 \text{ reads } 0000_{16}$ .

V208 reads its channel 1 voltage.

2.) Scan Table Pointer is set to 2<sub>16</sub>.

V243 reads 4001<sub>16</sub>. Enable bit is set. Channel 2 is indicated.

V243 outputs its channel 2 voltage.

V252 reads 0001<sub>16</sub>. Enable bit is not set.

V252 waits.

V208 reads 0001<sub>16</sub>.

V208 reads its channel 2 voltage.

- 17.) Scan Table Pointer is set to 2E<sub>16</sub>.

- 24.) Scan Table Pointer is set to 2E<sub>16</sub>.

V243 reads 8007<sub>16</sub>. End of list bit is set. Enable bit is not set.

V243 waits for next tick of MUX-bus clock to start at beginning of Scan Table

V252 reads C007<sub>16</sub>. End of list bit is set. Enable bit is set. Channel 8 is indicated. V252 outputs its channel 8 voltage, and waits for next tick of MUX-bus clock to start at beginning of Scan Table.

V208 reads 8007<sub>16</sub>. End of list bit is set.

V208 reads its channel 24 voltage and waits for next tick of MUX-bus clock to start at beginning of Scan Table.

The Scan RAM contains the Scan Table that must be setup properly on all MUX-bus modules. The Scan RAM is 2048 words long, and the Scan Table is a subset of the Scan RAM. Each module scans through its Scan Table sequentially at 200 Khz. At any time, the current data in the list dictates which module is to connect a channel to the MUX-bus.

The following is a list of steps to follow when setting up MUX-bus. There is also a programming example of this procedure called "setup()" in Appendix B (page B6).

# Step 1.) Get access to Scan RAM.

Before the Scan Table can be written into Scan RAM, the V243 and the V208 must be put in "setup" mode by resetting the ADSEL bit in the Configuration Register. Once a module is put in "setup" mode, MUX-bus is halted and access is allowed to that module's Scan RAM. If access to the Scan RAM is attempted while in "run" mode, the V243 will indicate it was unable to comply by asserting a bus error. As a general rule, the V208 or any other receiving MUX-bus module, should be the FIRST to be put in "setup" mode, and the LAST to be put in "run" mode.

# Step 2.) Write Scan Table into Scan RAM.

The Scan Table consists of the enable bit, a channel number, and an end of list bit. The Scan Table is organized the same on all modules whether it sources or receives voltages on the MUX-bus.

Bit 14 is the enable bit that connects the specified channel to MUX-bus. The enable bit must be set on only one sourcing module at any one time in the Scan Table (only one voltage may be out on MUX-bus at one time). If this rule is not implemented correctly, an overlap condition will occur once MUX-bus is started.

The channel is specified by the first 7 bits of Scan RAM. However, not all 100 channels (96 differential signals plus 4 isothermal references) of the V243 are available at any one time. The MUX-bus has four analog paths (labeled A through D) and is distributed evenly across all 100 channels of the V243. MUX-bus has these four distinct paths to increase bandwidth and lengthen settling time for better overall accuracy. The restriction, however, is that not all channels are available at any time. The very first channel in the Scan Table must be available on Path A, and the next channel from Path B, and so on. The Scan Table must continue to follow this  $A \rightarrow B \rightarrow C \rightarrow D$  order.

Here is the list of the paths and what channel is available from each. Please notice that the channels available on a path increment by four (the number of paths). These channels are distributed the same on all signal conditioning modules using MUX-bus.

| Path B Channels 2,6,10,14,18,98 are available. Path C Channels 3,7,11,15,19,99 are available. Path D Channels 4,8,12,16,20,100 are available. | Equation: $4N + 1$<br>Equation: $4N + 2$<br>Equation: $4N + 3$<br>Equation: $4N + 4$<br>where $N = 0$ to $23$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

Bit 15 is the end of list bit. This bit must be set on the last location of the Scan Table on all MUX-bus modules.

# Step 3.) Startup MUX-bus.

Finally, all modules using MUX-bus should be put in "run" mode starting with the signal conditioning modules (V243, V252, etc) first. The V208 must be the last module to be put in "run" mode.

# **MUX-bus Rules**

Should an overlap condition occur on a MUX-bus module, most likely one of the following rules were not implemented properly.

Rule #1.) The V208 must be the FIRST to be put in "setup" mode and the LAST to be put in "run" mode. This ensures that all MUX-bus modules remain in sync.

Rule #2.) The Enable bit should be set in only ONE module and any given Scan Table location. This ensures that only one module outputs a channel out on MUX-bus at one time.

Rule #3.) The End of List bit should be set in EVERY module at the same Scan Table location. All MUX-bus modules must have the same Scan Table size. This ensures modules remain in sync.

Rule #4.) The channels in the Scan Table must follow the MUX-bus path order. The Scan Table must continue to follow this  $A \rightarrow B \rightarrow C \rightarrow D$  order. (see Table 2 on page 17 for a more detailed explanation)

# **Overlap Detect Checklist**

Should an overlap condition occur on a MUX-bus module, this detailed list may help in finding the specific cause of the overlap condition.

Cause #1.) If an overlap occurred on only 1 MUX-bus module, then that module was programmed to output a channel at an inappropriate time. To increase bandwidth of MUX-bus and improve accuracy, MUX-bus has 4 distinct paths (A through D). However, any given channel on any given module is available only to one path. MUX-bus must run in order from Path A through to Path D. The following table gives an example of a properly programmed Scan Table.

TABLE 2 - V243 Scan Table, MUX-bus Path

|      | A24 Offset          | MUX-bus Path | Available Channels | Data                             | Channel Enabled |

|------|---------------------|--------------|--------------------|----------------------------------|-----------------|

|      |                     | •            |                    |                                  |                 |

|      |                     |              |                    |                                  |                 |

|      |                     |              |                    |                                  |                 |

|      | $20\mathrm{E}_{16}$ | Path D       | 4,8,12,16,100      | 0100 0000 0000 01112             | V243 Channel 8  |

|      | $20C_{16}$          | Path C       | 3,7,11,15,99       | 0100 0000 0000 0110 <sub>2</sub> | V243 Channel 7  |

|      | 20A <sub>16</sub>   | Path B       | 2,6,10,14,98       | 0100 0000 0000 01012             | V243 Channel 6  |

| ijā. | 208 <sub>16</sub>   | Path A       | 1,5,9,13,97        | 0100 0000 0000 0100 <sub>2</sub> | V243 Channel 5  |

|      | $206_{16}$          | Path D       | 4,8,12,16,100      | 0100 0000 0000 00112             | V243 Channel 4  |

|      | 204 <sub>16</sub>   | Path C       | 3,7,11,15,99       | 0100 0000 0000 00102             | V243 Channel 3  |

| . "  | $202_{16}$          | Path B       | 2,6,10,14,98       | 0100 0000 0000 00012             | V243 Channel 2  |

|      | $200_{16}$          | Path A       | 1,5,9,13,97        | 0100 0000 0000 0000 <sub>2</sub> | V243 Channel 1  |

|      |                     |              |                    | I .                              |                 |

Cause #2.) If an overlap occurred on two MUX-bus modules, then one of two possibilities caused the overlap. One possibility is that both modules were programmed to output a channel at an inappropriate time (see Cause #1). The other possibility is that two MUX-bus module tried to output voltages at the same time. This would occur if the enable bit in the Scan Table was set at the same location on those two modules.

Cause #3.) If an overlap occurred on multiple, but not all, MUX-bus modules, then most likely a combination of Causes #1 and #2 occurred.

Cause #4.)If an overlap occurred on all MUX-bus modules, then one of two possibilities caused the overlap. One possibility is that the V208 was not the last to be put in "run" mode. The other possibility is that the End of List bit was not set at the same location in each of their Scan Tables.

TABLE 3 - Calibration Register Values

| Cal Voltage | On board Source    | MUX bus Source     |

|-------------|--------------------|--------------------|

| +10.0 V     | 8091 <sub>16</sub> | 0091 <sub>16</sub> |

| +5.0 V      | 80A1 <sub>16</sub> | 00A1 <sub>16</sub> |

| +2.0 V      | 80C1 <sub>16</sub> | 00C1 <sub>16</sub> |

| +1.0 V      | 8092 <sub>16</sub> | 0092 <sub>16</sub> |

| +0.5 V      | 80A2 <sub>16</sub> | 00A2 <sub>16</sub> |

| +0.2 V      | 80C2 <sub>16</sub> | 00C2 <sub>16</sub> |

| +0.1 V      | 8094 <sub>16</sub> | 0094 <sub>16</sub> |

| +0.05 V     | 80A4 <sub>16</sub> | 00A4 <sub>16</sub> |

| +0.02 V     | 80C4 <sub>16</sub> | 00C4 <sub>16</sub> |

| +0.01 V     | 8098 <sub>16</sub> | 0098 <sub>16</sub> |

| +0.005 V    | 80A8 <sub>16</sub> | 00A8 <sub>16</sub> |

| +0.002 V    | 80C8 <sub>16</sub> | 00C8 <sub>16</sub> |

| -0.002 V    | 8148 <sub>16</sub> | 0148 <sub>16</sub> |

| -0.005 V    | 8128 <sub>16</sub> | 0128 <sub>16</sub> |

| -0.01 V     | 8118 <sub>16</sub> | 0118 <sub>16</sub> |

| -0.02 V     | 8144 <sub>16</sub> | 0144 <sub>16</sub> |

| -0.05 V     | 8124 <sub>16</sub> | 0124 <sub>16</sub> |

| -0.1 V      | 8114 <sub>16</sub> | 0114 <sub>16</sub> |

| -0.2 V      | 8142 <sub>16</sub> | 0142 <sub>16</sub> |

| -0.5 V      | 8122 <sub>16</sub> | 0122 <sub>16</sub> |

| -1.0 V      | 8112 <sub>16</sub> | 0112 <sub>16</sub> |

| -2.0 V      | 8141 <sub>16</sub> | 0141 <sub>16</sub> |

| -5.0 V      | 8121 <sub>16</sub> | 0121 <sub>16</sub> |

| -10.0 V     | 8111 <sub>16</sub> | 0111 <sub>16</sub> |

Note: For best results, use the on board source for the calibration voltages. The module is calibrated using its on board source.

### **Module Calibration**

In order to achieve the high degree of accuracy of the V243, error coefficients for both offset and gain are stored in the Correction Table (non-volatile RAM) on the V243.

Coefficients are stored for the calibrator to compensate for any gain error. These coefficients are applied in software during channel calibration to compute the true voltage applied to a channel during gain calibration. These coefficients are stored in the Correction Table (page 37) starting at A24 offset 2010<sub>16</sub>.

Coefficients are also stored to compensate for channel to channel offset errors. These coefficients are applied during channel offset calibration and are stored starting at A24 offset 2040<sub>16</sub>.

It is recommended that this calibration procedure be performed approximately every six months. The calibration date is also stored in the Correction Table to help track the last calibration date. The date is stored at the beginning of the Correction Table starting at A24 offset  $2000_{16}$ .

The following is a list of steps to follow in performing the V243 module calibration. There is also a programming example in Appendix B which performs the module calibration called "Module.c" (page B11). The documented code example will refer directly to the following steps:

- 1. The CAL strap must be moved to the enabled position (page 4).

- 2. The V243 should have a minimum of a 30 minute warm-up period.

- 3. Connect CAL OUT (pins 32 and 66 of any front panel connector) to a precision voltage meter.

- 4. Set all channels of the V243 to the front panel connectors. This can be done by writing all Prefilter Gain Registers with a 0.

- 5. Gain Calibration repeat steps 5a to 5c for all 12 differential, calibrator voltages. In the following equation, these expected calibrator voltages are referred to as CALIBRATOR ranging from 10 volts to 2 mV. The calibrator voltages are set by writing to the Calibration Register (Operational register in A24 space at offset 2<sub>16</sub>). A table of the precise register setting is available on page 17. Make sure to also set bits 15 and 13 of the Calibration Register to use the internal voltage reference and to enable calibration voltage out of the front panel connectors. Also, make sure to wait for the calibrator voltage to settle before any measurements are taken.

- a) Use a precision meter to measure the positive calibration voltage (average 10 points). The measured positive calibration voltage is referred to as PCAL in the equation from step 5c.

- b) Use a precision meter to measure the negative calibration voltage (average 10 points). The measured negative calibration voltage is referred to as NCAL in the equation from step 5c.

Store the error coefficient into the Correction Table (page 37) as a 16-bit signed integer according to the following equation:

$$GAINCOEFFICIENT = \left(\frac{PCAL - NCAL}{CALIBRATOR \bullet 2} - I\right) 10^{6}$$

Please note: Must wait a minimum of 3 ms after writing coefficient before writing again.

6. If offset calibration is unnecessary, skip to step #8.

7. Offset Calibration - for every channel repeat steps 7a through 7g.

- a) Connect all channels to the front panel connectors with 10 Hz filters and First Stage Gain set to 100. This can be done by writing all Prefilter Gain Registers with a 2<sub>16</sub>. Wait for filters to settle to 16-bit accuracy.

- b) Set the second stage gain for all channels to a gain of 20. This can be done by writing 4 to all Post Gain Registers.

- c) Measure the front panel offset voltage (RT0) using the V208. Use this equation to convert the COUNTS read from the V208 into voltage RTO. This front panel ground measurement is referred to as FP OFFSET in the equation in step 7g.

$$VOLTAGE(RTO) = (COUNTS - 32768) \circ 312.5 \mu Volts$$

- d) Connect all channels to the calibrator. The channels should still have the 10 Hz filters selected and the First Stage Gain set to 100. This can be done by writing all Prefilter Gain Registers with a 4002<sub>16</sub>.

- e) Set the calibrator voltage to ground and wait for filters to settle to 16-bit accuracy.

- f) Measure the calibrator offset voltage (RTO) using the equation from step 7c. The calibrator ground measurement is referred to as CAL OFFSET in the equation in step 7g.

- g) Store the offset error coefficient into the Correction Table (page 37) as a 16-bit signed integer using the following equation:

$$OFFSETCOEFFICIENT = \left(\frac{FPOFFSET - CALOFFSET}{2000}\right)10^{9}$$

Please note: Must wait a minimum of 3 ms after writing each coefficient before writing again.

8. Store calibration date into the Correction Table (page 37).

Please note: Must wait a minimum of 3 ms after writing each part of the date before writing again.

#### Channel Calibration

Once the module has been calibrated, each channel on the V243 can be calibrated using the onboard calibrator all under software control. Offset and gain error coefficients for each channel must be stored in software and be applied to all voltage readings from those channels. It is important not to confuse these error coefficients in software with those stored in the Correction Table on the V243. The error coefficients in the Correction Table are used during the channel calibration only. The following is a list of steps to follow in performing the V243 channel calibration:

- 1. The V243 should be allowed at least a 30 minute warm-up period.

- 2. Setup all channels to the chosen gain and filter selection.

- 3. Gain Calibration for every channel, repeat steps 3a through 3f.

- Set the channel so it is set to the calibration voltage. This is done by setting bit 14 (only) of the Prefilter Gain Registers. Do not change the value of the other bits in this register.

- b) Set the calibration voltage so the channels have positive full scale voltage. The full scale voltage is dependent on the gain setting for that channel. The expected positive full scale calibration voltage will be referred to as POSCALEXPECTED in the following equation. The calibration voltage is set by writing to the calibration Register (Operational register in A24 space at offset 2<sub>16</sub>). A table of the register settings is available of page 17. Also, be sure to wait for the voltage to settle to 16-bit accuracy once the calibration voltage is set.

- c) Measure the positive full scale voltage (average a minimum of 20 points). Use the equation below to convert the COUNTS read from the V208 into voltage RTO. The measured positive full scale calibration voltage is referred to as POSCALMEASURED in the equation.

# $VOLTAGE(RTO) = (COUNTS - 32768) \circ 312.5 \mu Volts$

- d) Set the calibration voltage so the channels have negative full scale voltage. The full scale voltage is dependent on the gain setting for that channel. The expected negative full scale calibration voltage will be referred to as NEGCALEXPECTED in the equation in step 3f. The calibration voltage is set by writing to the Calibration Register (Operational register in A24 space at offset 2<sub>16</sub>). A table of the register settings is available of page 17. Also, be sure to wait for the voltage to settle to 16-bit accuracy once the calibration voltage is set.

- e) Measure the negative full scale voltage (average a minimum of 20 points) using the equation in step 3c. The measured negative full scale calibration voltage is referred to as NEGCAL<sub>MEASURED</sub> in the equation in step 3f.

f) Read the gain error for the calibrator voltage from the Correction Table (page 37). The gain error correction term is referred to as GAIN COEF in the following equation.

$$GAIN = \frac{POSCAL_{MEASURED} - NEGCAL_{MEASURED}}{\left(POSCAL_{EXPECTED} - NEGCAL_{EXPECTED}\right) \bullet \left(1 + GAINCOEF \bullet 10^{-6}\right)}$$

Record the gain for the channel as calculated above.

- 4. Offset Calibration for every channel

- a) Set the calibration voltage to ground. Write 4000<sub>16</sub> to the Calibration Register (Operation register in A24 space at offset 2<sub>16</sub>). Wait for the filter to settle to 16-bit accuracy.

- b) Measure the offset voltage (average a minimum of 20 points) using the equation in step 3c. The measured offset voltage is referred to as OFFSET<sub>MEASURED</sub> in the following equation.

- c) Read the offset error for the calibrator voltage from the Correction Table (page 37). The offset error correction term is referred to as OFFSET COEF in the following equation.

$$OFFSET = \frac{OFFSET_{MEASURED}}{GAIN} + \left(OFFSETCOEF \bullet 10^{-9}\right)$$

Record the offset error for the channel as calculated above.

5. Applying the channel calibration coefficients - Example with V208

The V208 represents voltage in an offset binary format. In the following two equations, this variable will be referred to as COUNTS.

When calibration is unnecessary, the gain is derived simply from the gain settings in the Prefilter Gain and Post Filter Gain Registers. This uncalibrated gain is represented with the variable GAINUNCALIBRATED in the following equation. Convert counts to uncalibrated voltage using the following equation:

$$UNCALIBRATEDVOLTAGE = \frac{\left(COUNTS - 32768\right) \bullet 312.5 \,\mu Volts}{GAIN_{UNCALIBRATED}}$$

For best accuracy, convert counts to calibrated voltage using the following equation:

$$CALIBRATEDVOLTAGE = \frac{\left(COUNTS - 32768\right) \bullet 312.5 \,\mu Volts}{GAIN} - OFFSET$$

# Suggestions for Highest Accuracy

- 1.) For best accuracy, it is recommended (but not necessary) to keep channels with similar gains grouped together.

- 2.) For best accuracy, it is recommended (but not necessary) that channels be organized with the gain set in decreasing order. The MUX-bus scan list should also follow this order.

- 3.) Unused channels should be grounded.

- 4.) Refer to Appendix A for a discussion of the recommended grounding scheme. In general, the best solution is to use shielded balanced pair wire with the shield grounded at the V243.

# V243 Configuration Registers

# ID / Logical Address Register

| <sup>00</sup> 16 |     |     |     |     | 11  |       |     | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00    |

|------------------|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| (R)              | (0) | (1) | (0) | (0) | (1) | (1)   | (1) | (1) | (0) | (0) | (1) | (0) | (1) | (0) | (0) | (1)   |

|                  |     |     |     |     | ,   | , , , |     |     |     |     |     |     |     |     |     | Value |

Bit(s) Mnemonic

Meaning

15,14 Device Class

This is an Extended Register-Based Device.

13,12 Address Space

This module requires the use of A16/A24 address space.

11-00 Manufacture's ID

$3881 (F29_{16})$  for KineticSystems.

| $^{00}16$ | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07  | 06  | 05  | 04  | 03         | 02  | 01  | 00    |

|-----------|----|----|----|----|----|----|----|----|-----|-----|-----|-----|------------|-----|-----|-------|

| (W)       |    |    |    |    |    |    |    |    | LA7 | LA6 | LA5 | LA4 | LA3        | LA2 | LA1 | LA0   |

|           |    |    |    |    |    |    |    |    |     |     |     |     | <i>(</i> ) | D   | тт  | T 7 1 |

() Power Up Value

For WRITE transactions, bits fifteen through eight are not used. These bits may be written with any data pattern. In Dynamically Configured systems (and the Logical Address switches were set to a value of 255), bits seven through zero are written with the Logical Address value. This register is used by the resource manager to dynamically set a module's logical address.

# **Device Type Register**

| $^{02}16$ | 15                | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |  |

|-----------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| (R)       | (1)               | (0) | (0) | (1) | (0) | (0) | (1) | (0) | (0) | (1) | (0) | (0) | (0) | (0) | (1) | (1) |  |

|           | () Power Up Value |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |  |

This READ ONLY register returns 9243<sub>16</sub>.

Bit(s) Mnemonic

Meaning

15-12 Required Memory

The V243 requires 16 Kilo bytes of additional memory space.

11-00 Model Code

Identifies this device as a V243 (243<sub>16</sub>).

# Status/Control Register

| 0416    | 15                | 14           | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06                                    | 05  | 04           | 03           | 02   | 01   | 00                   |        |

|---------|-------------------|--------------|-----|-----|-----|-----|-----|-----|-----|---------------------------------------|-----|--------------|--------------|------|------|----------------------|--------|

| (Mixed) | A24<br>ENA<br>(0) | Modid<br>(0) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1)                                   | (1) | (1)          | Ready<br>(0) | (1)  | (1)  | Soft<br>Reset<br>(0) | ŀ      |

|         |                   |              |     |     |     |     |     |     |     | · · · · · · · · · · · · · · · · · · · |     | <del> </del> | ()           | Powe | r Un | Value                | '<br>e |

The bit assignments for the Status/Control register are defined as follows:

| Bit(s) | Mnemonic   | Meaning                                                                                                                                                                                                                                                                                                                                                                       |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | A24 ENA    | This bit is written with a "1" to enable A24 addressing and reset to "0" to disable these registers. This bit must be set to allow access to the module's Operational Registers. Reads of this bit indicate its current state. This bit is reset to "0" by the assertion of SYSRESET*. This bit is set by the resource manager once the offset register has been written.     |

| 14     | Modid*     | This read only bit is set to a "1" if the module is <u>not</u> selected with the MODID line on P2. A "0" in this bit location indicates the device is selected via a high state on its P2 MODID line. This bit is used by the resource manager to dynamically configure the V243.                                                                                             |

| 13-04  | Not Used   | These bits are not used and are read as "1s".                                                                                                                                                                                                                                                                                                                                 |

| 03     | Ready      | A "1" in this bit indicates the successful completion of register initialization.                                                                                                                                                                                                                                                                                             |

| 02-01  | Not Used   | These bits are not used and are read as "1s".                                                                                                                                                                                                                                                                                                                                 |

| 00     | Soft Reset | Writing a "1" to this bit forces the device into the Soft Reset State. While in this state, the module will only allow access to its Configuration Registers. Writing a "0" to this bit will the signal the V243 to begin executing its self test. This bit must be cleared along with the Pass and Ready bits set before any access to the Operational Registers is allowed. |

# Offset Register

| $^{06}16$ | 15        | 14        | 13        | 12        | 11        | 10        | 09       | 08       | 07       | 06       | 05       | 04       | 03       | 02       | 01       | 00       |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| (RW)      | OFF<br>15 | OFF<br>14 | OFF<br>13 | OFF<br>12 | OFF<br>11 | OFF<br>10 | OFF<br>9 | OFF<br>8 | OFF<br>7 | OFF<br>6 | OFF<br>5 | OFF<br>4 | OFF<br>3 | OFF<br>2 | OFF<br>1 | OFF<br>0 |

|           | (0)       | (0)       | (0)       | (0)       | (0)       | (0)       | (0)      | (0)      | (0)      | (0)      | (0)      | (0)      | (0)      | (0)      | (0)      | (0)      |

|           |           |           |           |           |           |           |          |          |          |          |          |          | ()       | D        | T T      | T7_1     |

() Power Up Value

After SYSRESET\* and prior to self test all bits are reset to "0". Otherwise, a read or write

$$A24BASEADDRESS = OFF[15:0] \bullet 100_{16}$$

defines the base address of the module's A24 registers.

# Attribute Register

| $^{08}16$ | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02         | 01         | 00         |

|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------------|------------|------------|

| (R)       | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | IR*<br>(0) | IH*<br>(1) | IC*<br>(0) |

|           |     |     |     |     |     |     |     |     |     |     |     |     | ()  | Powe       | r Up       | Value      |

This read only register returns FFFA<sub>16</sub> on READ transactions. Write transactions to this register have no effect and its usage is reserved for future definition.

| Bit(s) | Mnemonic | Meaning                                                                                       |

|--------|----------|-----------------------------------------------------------------------------------------------|

| 15-03  | Reserved | These bits are read as "1s" and reserved for future definition.                               |

| 02     | IR*      | This bit is read as a "0" to signify that the $V243$ is capable of generating interrupts.     |

| 01     | IH*      | This bit is read as a "1" and indicates the V243 is not capable of Interrupt Handler Control. |

| 00     | IS*      | This bit is set to "0" to indicate the V243 has Interrupt Status Reporting capability.        |

# Serial Number High

| <sup>0A</sup> 16 | 15               | 14               | 13               | 12               | 11               | 10               | 09               | 08               | 07               | 06               | 05               | 04               | 03               | 02               | 01               | 00               |   |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|---|

| (R)              | SER<br>31<br>(?) | SER<br>30<br>(?) | SER<br>29<br>(?) | SER<br>28<br>(?) | SER<br>27<br>(?) | SER<br>26<br>(?) | SER<br>25<br>(?) | SER<br>24<br>(?) | SER<br>23<br>(?) | SER<br>22<br>(?) | SER<br>21<br>(?) | SER<br>20<br>(?) | SER<br>19<br>(?) | SER<br>18<br>(?) | SER<br>17<br>(?) | SER<br>16<br>(?) |   |

| Serial           | Num              | her '            | Low              |                  |                  |                  |                  |                  |                  |                  |                  |                  | ()               | Powe             | r Up             | Value            | е |

| $^{0}C_{16}$ | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| (R)          | SER |

|              | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|              | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) | (?) |

() Power Up Value

These READ ONLY registers indicate the serial number of the module. Each module is These READ ONLY registers indicate the serial number of the module. Each module is given a unique serial number. The serial number is represented by a 32-bit unsigned integer. The least significant bits (LSBs) reside in the Serial Number Low register while the most significant bits (MSBs) are in the Serial Number High register. Writing to these registers will have no effect and its use is reserved. For example, assume the module's serial number is  $10064_{16}$  (65636). A read of the Serial Number High register returns  $0001_{16}$  (1 => 1 \* 65536); and the Serial Number Low register returns  $0064_{16}$  (100).

#### Version Number Register

| $^{0}\mathrm{E}_{16}$ | 15  | 14          | 13        | 12  | 11  | 10          | 09              | 08  | 07 | 06           | 05       | 04  | 03 | 02          | 01           | 00    |

|-----------------------|-----|-------------|-----------|-----|-----|-------------|-----------------|-----|----|--------------|----------|-----|----|-------------|--------------|-------|

| (R)                   | Fir | mware<br>(' | Version?) | n # | Fir | ınware<br>( | e Revisi<br>(?) | on# | He | rdware<br>() | · Versio | n # | На | rdware<br>( | Revisi<br>?) | on#   |

|                       |     |             |           |     |     |             |                 |     |    |              |          |     | () | Powe        | r Un         | Value |

This READ ONLY register indicates the hardware and firmware revision number of the module. A write to this register has no effect on its contents. The fields of this register are explained as follows:

| <u>Bits</u> | Mnemonic            | Meaning                  |

|-------------|---------------------|--------------------------|

| 15-12       | Firmware Version#   | Firmware Version Number  |

| 11-08       | Firmware Revision#  | Firmware Revision Number |

| 07-04       | Hardware Version #  | Hardware Version Number  |

| 03-00       | Hardware Revision # | Hardware Revision Number |

The combination of Firmware Version Number and Firmware Revision Number indicate the module's firmware version level. These two fields contain two four bit integers and are joined to form the level.

The combination of Hardware Version Number and Hardware Revision Number indicate the module's hardware version level. These two fields contain two four bit integers and are joined to form the level.

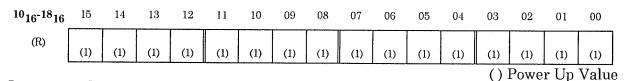

#### Reserved

#### Interrupt Status Register

| <sup>1A</sup> 16 | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07 | 06 | 05 | 04            | 03     | 02 | 01 | 00 |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|---------------|--------|----|----|----|

| (RW)             | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) |    |    | I  | Logical<br>FI | Addres | s  | ,  |    |

This READ ONLY register is defined as follows:

() Power Up Value

Bit(s) Mnemonic

Meaning

15-8 Reserved

These bits are read as "1s".

7-0 Logical Address

These bits contain the Logical Address of the V243 during an interrupt acknowledge cycle. These bits are read as all ones during a non-interrupt acknowledge cycle.

# Interrupt Control Register

| 1C <sub>16</sub> | 15     | 14  | 13  | 12  | 11  | 10  | 09  | 08                  | 07               | 06  | 05   | 04          | 03   | 02   | 01   | 00    |   |

|------------------|--------|-----|-----|-----|-----|-----|-----|---------------------|------------------|-----|------|-------------|------|------|------|-------|---|

| (RW)             | (1)    | (1) | (1) | (1) | (1) | (1) | (1) | Over<br>Mask<br>(1) | IREN<br>*<br>(1) | (1) | IRQ2 | IRQ1<br>(1) | IRQ0 | (1)  | (1)  | (1)   |   |

| Iloina           | thia r |     |     |     | -1  |     |     | 3 (*                | ,                |     | I    |             | ()   | Powe | r Up | Value | ) |

Using this register to control interrupts is defined as follows:

| Bits(s) | <u>Mnemonic</u> | Meaning                                                                                                                                                                         |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 - 09 | Not Used        | These bits are not used and should be written as "1s"                                                                                                                           |

| 8       | Over Mask       | A "1" in this bit masks (prevents) an overlap from Generating an interrupt request. This bit must be written with a "0" to allow the overlap to generate an interrupt.          |

| 7       | IREN*           | A one in this bit is used to disable interrupt generation. This bit prevents <u>any</u> source from generating an interrupt. A zero in this field enables interrupt generation. |

| 6       | Not Used        | This bit is reserved for use during interrupt handling. Since the V243 is not capable of interrupt handling, this bit should always be written with a "1".                      |

| 5-3     | IRQ2*-IRQ0*     | This 3-bit field selects the VXIbus interrupt line associated with the interrupt according to the following table:                                                              |

| table: |                |   |                           |

|--------|----------------|---|---------------------------|

|        | TRLQ*<br>(D04) |   | Interrupt Request<br>Line |

| 0      | 0              | 0 | IRQ7                      |

| 0      | 0              | 1 | IRQ6                      |

| 0      | 1              | 0 | IRQ5                      |

| 0      | 1              | 1 | IRQ4                      |

| 1      | 0              | 0 | IRQ3                      |

| 1      | 0              | 1 | IRQ2                      |

| 1      | 1              | 0 | IRQ1                      |

| 1      | 1              | 1 | Disconnected              |

2-0 Not Used

These bits are reserved for selecting an interrupt handler line. The V243 does not have interrupt handler capabilities, these bits should always be written with "1s".

#### Subclass Register

| <sup>1E</sup> 16 | 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02   | 01    | 00    |      |

|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-------|-------|------|

| (R)              | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1) | (1)  | (1)   | (0)   | ine. |

|                  |     |     |     |     |     |     |     |     |     |     |     |     | ()  | Powe | er Up | Value | Э    |

Reads of this register return FFFE<sub>16</sub>. Writes to this register have no effect. The read contents are defined as follows:

# Bit(s) Meaning This bit indicates that the V243 is a VXIbus defined Extended Device. These bits indicate that this is an Extended Register Based Device.

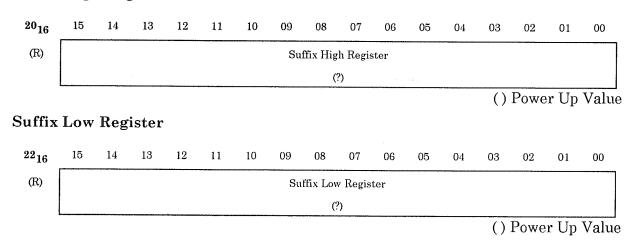

#### Suffix High Register

The following two registers are KineticSystems defined and hold the module's suffix. The suffix determines the particular option of the module. This information can be used to remotely establish available channel count, filtering options, etc. of the module. For further information on each option, refer to the Ordering Information section of this manual.

The module's suffix is always composed of four ASCII characters. The Suffix High register contains the first two characters; while, the last two characters are in the Suffix Low register. For instance, assume the module is a model V243-VA91. The module's suffix is "VA91". Converting this to ASCII yields  $56413931_{16}$ .

#### **User Defined Registers**

Offsets  $24_{16}$  through  $3E_{16}$  are READ/WRITE registers and may be used to store user defined data. These registers are contained in non-volatile EEPROM. Special Note: Special care must be taken while writing information into these. Once a register has been written, a minimum of 3mS must pass before any User Defined Register or Correction Table Registers may be read or written to.

## V243 Operational Registers

# Configuration Register (Mixed)

| $^{00}16$ | 15  | 14  | 13  | 12                                    | 11           | 10           | 09           | 08           | 07           | 06           | 05           | 04  | 03   | 02    | 01   | 00    |        |

|-----------|-----|-----|-----|---------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-----|------|-------|------|-------|--------|

| (Mixed)   | (1) | (1) | (1) | (1)                                   | Con 3<br>(?) | Con 2<br>(?) | Con 1<br>(?) | Con 0<br>(?) | Therm<br>(0) | Ovrlp<br>(0) | Adsel<br>(0) | (1) | (1)  | (1)   | (1)  | (1)   |        |