# **Model V205**

32-channel, 10 Msample/s, 16-Bit ADC

## User's Manual

November 22, 2000

(C) 2000

Copyright by

KineticSystems Company, LLC

Lockport, Illinois

All rights reserved

## \*\*\*Special Option\*\*\*

Model V205-S001

32-channel, 10 Msample/s, 16-Bit ADC

November 22, 2000

© 2000 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

Page 1S of 2S

## \*\*\*Special Option\*\*\*

#### Model V205-S001

The Model V205-S001 is the same as the V205-AA11 except it has been modified to have a  $10\ K$  ohm input impedance.

${\bf ***Special\ Option ***}$

Model V205-S002

32-channel, 10 Msample/s, 16-Bit ADC

November 6, 2000

© 2000 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

Page 1S of 2S

## \*\*\*Special Option\*\*\*

## Model V205-S002

The Model V205-S002 is the same as the V205-CA11 except it has been modified to have 32-channel, 2.5 MHz, 16-Bit Sigma Delta ADC with 50 ohm input impedance instead of 500 ohm.

# Contents

| ABOUT THIS MANUAL                                  | 1   |

|----------------------------------------------------|-----|

| Organization                                       | 1   |

| Glossary                                           |     |

| CHAPTER 1: INTRODUCTION                            | 3   |

| ABOUT THE V205                                     |     |

| Features                                           | 3   |

| Applications                                       | 3   |

| General Description                                | 3   |

| Ordering Information                               | 3   |

| Board Specifications.                              | 4   |

| DETAILED DESCRIPTION                               | 5   |

| ADC Section                                        | 6   |

| Input Bandwidth and Sample Rate                    | 0   |

| Clock/Trigger Options                              | /   |

| Modes of Operation                                 |     |

| Cascading Multiple Boards                          |     |

| Related products                                   | 9   |

| Unpacking the V205                                 | 10  |

| CITA INCIDENTA A TRICOGRAFIA A TRACOGRAFIA         | 10  |

| CHAPTER 2: INSTALLATION AND CONFIGURATION          | 11  |

| SETTING THE LOGICAL ADDRESS SWITCHES               | 11  |

| MODULE INSERTION                                   | 12  |

| MODULE CONFIGURATION                               |     |

| Setting the VXI Logical Address                    | 13  |

| CHAPTER 3: CONFIGURATION AND OPERATIONAL REGISTERS |     |

| CALL TERS. CONFIGURATION AND OPERATIONAL REGISTERS | 15  |

| ADDRESS SPACE                                      | 15  |

| STATIC AND DYNAMIC CONFIGURATION                   | 1.0 |

| COMMUNICATION PROTOCOL                             | 16  |

| REGISTER ADDRESSING                                | 1.0 |

| REQUIRED CONFIGURATION REGISTERS                   | 17  |

| 1D Register 00h                                    | 17  |

| Logical Address Register 00h                       | 1.9 |

| Device Type Register 02h                           | 18  |

| Status Register 04h                                | 18  |

| Control Register 04h                               | 10  |

| Offset Register 06h                                | 10  |

| ADDITIONAL CONFIGURATION REGISTERS                 | 20  |

| Autobie Register Von                               | 20  |

| Seriai Number Register 0Ah, 0Ch                    | 21  |

| version Number Register UEh                        | 21  |

| Interrupt Status Register IAh                      | 22  |

| Interrupt Control Register 1Ch                     | 22  |

| Subclass Register IEh                              | 23  |

| Sujjix Register 20h, 22h                           | 24  |

| Trigger Mapping Register 36h                       | 24  |

| OPERATIONAL REGISTERS                              | 26  |

| Status Register (SR) 00004h                        | 27  |

| Interrupt Mask Register (IMR) 00008h               | 28  |

| Control Register (CR) 0000Ch                       | 29  |

| Channel Count Register 00010h                      | 31  |

| Bujjer Length Register 00014h                      | 32  |

| Acquisition Count Register 00018h                  | 33  |

|                                                    |     |

| Model V205                                         | Contents |

|----------------------------------------------------|----------|

| Decimation Count Register 0001Ch                   | 34       |

| ADC Clock Frequency Register 00024h                |          |

| Arm Register 0002Ch                                | 35       |

| ADC Reset Register 00030h                          | 35       |

| Buffer Reset Register 00034h                       | 35       |

| Board Reset Register 00038h                        | 36       |

| Interrupt Configuration Register 1008Ch            | 36       |

| ADC Data 40000                                     | 36       |

| Using Diagnostic Mode                              |          |

| CHAPTER 4: PROGRAMMING THE INTERNAL CLOCK GENERATO | R38      |

| Introduction                                       |          |

| Programming Summary                                |          |

| Programming Register                               |          |

| VCO Programming Constraints                        |          |

| Program Register Example                           |          |

| Oscillator Programming Example                     |          |

| Order of Operations for Simple Acquisition         |          |

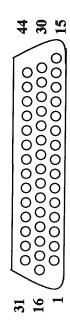

| APPENDIX A: CONNECTOR INFORMATION                  | 44       |

| Analog Input Connectors                            | 44       |

| Analog 1-16 Connector Details                      | 44       |

| Analog 1-16 Connector Signal Allocation            |          |

| Analog 17-32 Connector Details                     |          |

| Analog 17-32 Connector Signal Allocation           |          |

| P4 Local Bus Connector Details                     |          |

| P4 Local Bus Connector Signal Allocation           |          |

| WARRANTY                                           |          |

|            | FIGURES                                                    |    |

|------------|------------------------------------------------------------|----|

| Figure 1-1 | V205 Simplified Block Diagram                              | 4  |

| Figure 1-2 | V205 Analog Input Stage (One Channel Only)                 | 7  |

| Figure 2-1 | V205 Logical Address Switch Locations                      | 12 |

|            | TADI EG                                                    |    |

|            | TABLES                                                     |    |

| Table 3-1: | Relationship between the "m" Parameter and Required Memory | 15 |

| Table 3-2: | Interrupt Request Levels                                   | 23 |

| Table 3-3: | V205 Bits 11-8 Mapped Trigger Line                         | 25 |

| Table 3-4: | V205 3-0 Mapped Trigger Line Bits                          | 26 |

# **About This Manual**

## Organization

Chapter 1, *Introduction and General Description*, gives you a brief overview of the Model V205, lists items you need to get started, and explains how to safely unpack your module.

Chapter 2, *Installation and Configuration*, explains how to configure the V205 and correctly insert it into a C-size VXIbus mainframe.

Chapter 3, Configuration and Operational Registers, explain how to access and control the V205.

Chapter 4, *Programming Information*, gives you example setup procedures for preparing the V205 to acquire data.

Appendix A, explains V205 connector information.

Warranty, provides information that may be helpful in learning more about KineticSystems and its products, and in quickly reaching us.

## Glossary

Following is a glossary of some of the terms and conventions used throughout this manual:

An indicator that a register bit contains low-true data. For example, writing a "0" to a bit labeled Enable\* would cause a function to be enabled.

A16 Space The first 64 Kbytes of address space, accessible with 16-bit addressing.

configuration registers of VXI devices occupy 64-byte blocks of this address space. The Logical Address of a device determines which 64-byte block is associated with

that device.

A32 Space The 4 Gbyte address space, accessible with 32-bit addressing. A module can

request a block of this address space via information contained in its Configuration

registers. Operational registers, if present, reside in this space.

**Configuration** Setup registers located in **A16** space. Some are mandatory; some are optional. **Registers**

D16 A single 16-bit data transfer.

**D16 BLK** A block transfer of 16-bit words.

D32 A single 32-bit data transfer. Not all Slot-0 controllers support D32.

D32 BLK A block transfer of 32-bit words. Not all Slot-0 controllers support D32 BLK.

Device One of 255 devices that a VXIbus system can support. The term is often used

interchangeably with "module." The distinction is that a VXIbus module can

consist of more than one device.

Dynamic Addressing

The VXIbus addressing mode in which the address of a device is stored in a write-

able register. See also Static Addressing.

hexadecimal A base-16 number. The suffix, "h," indicates that a number is hexadecimal. For

example,  $1Ah = 26_{10}$ ;  $FFh = 255_{10}$ ;  $1000h = 4096_{10}$ .

Logical Address A VXIbus module's unique address. A VXIbus system has 254 logical addresses that are available. "0" is the address of the Slot-0 controller. "255" specifies that dynamic addressing be used to address that module.

Operational Registers

Setup and data-transfer registers that are located in A24 address space.

Resource Manager

Software that sets logical addresses and optimally configures Operational register addresses and memory-block addresses in a system. The manufacturer of the Slot-0

controller provides this software, often referred to as "RESMAN."

Static Addressing The VXIbus addressing mode in which the address of a device is stored in a switch

register. See also Dynamic Addressing.

# **Chapter 1: Introduction**

## **About the V205**

#### Features

- 8, 16 or 32 channels

- Simultaneous sampling at output rates up to 10 Msamples/s per channel

- External or programmable internal clock and trigger

- 1 megasample on-board buffer

- Multiple board synchronization

- Transient mode of data collection

- Pre- and post-trigger data collection (circular buffering)

## **Applications**

- Radar systems

- Sonar (hydroacoustic) systems

- High-speed communications systems

- High Energy Physics experiments

- Instrumentation requiring high-bandwidth analog conversion

## **General Description**

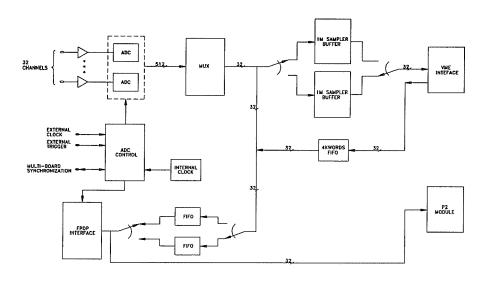

Figure 1 shows a simplified block diagram of the V205 board. The board uses 32 16-bit oversampling ADCs (Analog Devices AD9260) to provide simultaneous sampling at rates of up to 10.0 MSamples/sec. on each channel. The oversampling ratio of the ADC can be selected as 2, 4 or 8.

ADC data is buffered in the dual-ported buffer memories for read out via the VXIbus. The sampling clock and the trigger can be either internal or external. The internal ADC clock is user programmable in steps of less than 250Hz at the output rate. Whether the internal clock or an external clock is used, the frequency must be set to twice the desired oversampling rate (i.e., 16x, 8x, or 4x the output word rate). When the software device driver is used, the frequency provided by the user to the internal clock programming function is the actual output word rate required; the function takes care of multiplying this by the required factor.

The ADCs can only be operated in transient mode. In transient mode, a fixed number of samples are acquired upon each application of the trigger. Capture mode has two sub-modes; with pre-trigger data storage and without pre-trigger data storage. When using pre-trigger storage, the V205 stores samples continuously before the trigger and acquires a programmable number of samples following the trigger (to a maximum of 32,768 samples/channel if all 32 channels are active). When pre-trigger storage is not used, conversion starts at each application of the trigger and a programmable number of samples (again, to a maximum of 32,768) are acquired.

In transient mode, the acquisition count and buffer length must be programmed separately. When using capture mode without pre-trigger storage, the buffer length must be an integral multiple of the acquisition count. Thus, it is possible to perform multiple capture sequences at each occurrence of the trigger, until the buffer is filled to the programmed length.

The V205 board can generate VXIbus interrupts at any user programmed buffer length.

Figure 1-1 V205 Simplified Block Diagram

## **Ordering Information**

Model V205-AA11 8-channel, 10 MSa/s, 16-bit ADC Model V205-BA11 16-channel, 10 MSa/s, 16-bit ADC Model V205-CA11 32-channel, 10 MSa/s, 16-bit ADC

## **Board Specifications**

#### Specifications subject to change without notice.

#### **V205 Board Specifications**

**Analog Input**

Number of Analog Input Channels: 8, 16 or 32

Input Impedance:

500 Ohms

Full Scale Input:

$\pm 1.0 \, \mathbf{V}$

Maximum Input Sample Rate (Fs):

20 MHz

Oversampling Ratio:

2, 4, or 8

Maximum Input Signal Bandwidth:

0.430 x Fo (-0.1dB 8x Oversampling)

Maximum Input Signal Bandwidth

0.480 x Fo (-3.0dB 8x Oversampling)

Maximum Input Signal Bandwidth

0.410 x Fo (-0.1dB 4x Oversampling)

Maximum Input Signal Bandwidth

0.478 x Fo (-3.0 dB 4x Oversampling)

Maximum Input Signal Bandwidth

0.323 x Fo (-0.1dB 2x Oversampling)

Maximum Input Signal Bandwidth

0.453 x Fo (-3.0dB 2x Oversampling)

\*\*\*\*

where Fo = Fs/2, Fs/4 or Fs/8

Maximum Channel Output Rate:

2.5 MHz/ch. for 32 channels (2x oversampling)

5.0 MHz/ch. for 16 channels (4x oversampling)

10.0 MHz/ch. for 8 channels (8x oversampling)

0.125 kHz/ch. for 32 channels (8x oversampling using

external clock)

24 kHz/ch. For 32 channels (8x oversampling using

Minimum Channel Output Rate:

internal clock)

Maximum Decimation:

256

Settling Time:

312/Fs (8x oversampling)

112/Fs (4x oversampling)

26/Fs (2x oversampling)

Signal/(Noise+Distortion+Crosstalk):

>TBD (Fs/8)

>TBD (Fs/4)

>TBD (Fs/2)

Inter-channel Cross-talk:

<TBD

On-board Storage:

1 Msample

(32 Ksample/channel, all 32 chan's active

#### **V205 Board Specifications**

General

VXIbus Interface:

A32/D32/Slave

Environmental:

Temp: 0° to +50°C operating (at entry point of forced

air, approximately 490 LFM)

-40° to +85°C Storage

Humidity <95% non-condensing

Power:

6.75 Amps @ +5 V

0.3 Amp @ +12 V

0.3 Amp @ -12 V

## **Detailed Description**

#### **ADC Section**

The V205 board uses 32 16-bit ADCs (Analog Devices AD9260). The maximum input clock frequency for the ADC is 20 MHz. Thus, the maximum output rate (2x oversampling V205 mode) if 10 Msamples/sec for each channel. Note that, at an oversampling ratio of 2, the V205 will operate with a maximum of 8 channels, and at an oversampling ratio of 4, the V205 with a maximum of 16 channels, as a result of limited bus bandwidth on the board. The minimum sampling rate for the ADCs is 1.0 kHz, giving a minimum output rate of 125 Hz in 8x oversampling mode with an external clock source of 2 kHz. However, the ADC data stream may be subsequently decimated by a factor of up to 256. Decimation is accomplished by storing one out of every N samples where N is programmable from 1 to 256. This programmable decimation feature should not be confused with the decimation provided on the chip that is carried out after digital filtering of the signals.

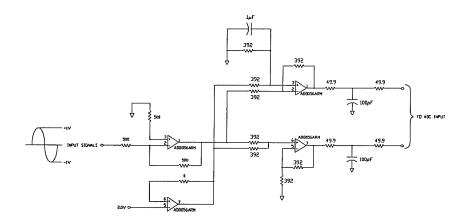

The board accepts unbalanced (single-ended) analog inputs with a full-scale input signal level of 2 Vpp; the input impedance is 500 Ohm. Figure 2 shows the input buffer stage for one channel. Two 44-pin connectors (marked P6 and P7) are provided on the front panel for applying the analog input signals.

Figure 1-2 V205 Analog Input Stage (One Channel Only)

# Input Bandwidth and Sample Rate

The AD9260 ADC chip employs three cascaded digital lowpass filters to achieve the desired decimation. The composite response of these filters governs the input signals bandwidth.

The choice of decimation (oversampling) ratio may be selected using the ADC Oversampling Ratio field of the V205 Control register. Further details on the converter characteristics are available from the manufacturer, Analog Devices, at the following website address:

http://products.analog.com/products/info.asp?product=AD9260

The outputs of the ADCs are combined to produce up to 32 32-bit words, depending on the number of channels selected to be active in the Channel Count register. The selected data are transmitted to the VXI buffer memory. The packed output data format is as follows:

| D15D0     |                               |

|-----------|-------------------------------|

| Channel 2 | Word 1                        |

| Channel 4 | Word 2                        |

|           | Word 2                        |

| Channel N | Word 2                        |

| Channel 2 | Word 2                        |

|           | Word 2                        |

|           | Channel 2 Channel 4 Channel N |

## Clock/Trigger Options

The V205 offers a number of clock and trigger options. The card has an internal sampling clock provided by a programmable oscillator giving a resolution of less than 1 kHz at the output rate, over the range 24kHz to 10 MHz. Alternatively, an external sampling clock may be applied at pin 25 of the P4 front panel connector. The minimum output rate using an external clock is 125 Hz (1kHz/8x oversample). In either case, the clock frequency must be set to twice the required oversampling frequency.

The trigger can be programmed to be internal (i.e., software controlled) or external. If using the external trigger, the user should supply a positive-going TTL pulse on pin 23 or the P4 connector, the pulse must be at least one sample period long. The trigger is internally synchronized to the sampling clock by the V205. Acquisition starts with the first valid data word after the application of the trigger.

Both external clock and trigger signals must conform to standard TTL levels and drive capability. The relevant connections are listed in a later section.

## Modes of Operation

Two modes of operation are provided in the V205 design:

- Transient mode without pre storage,

- Transient mode with pre storage.

In the transient mode *without* pre storage, data is acquired for a programmable number of samples following the application of each trigger. The maximum number of samples that can be stored for all active channels is 1048576 (32768 x 32). Because the size of the memory buffer, and the count of samples acquired are both programmable, multiple capture acquisitions may be stored in the V205 memory.

Important note: When using transient mode without pre-trigger storage, the memory buffer length programmed must always be an integral number of acquisition counts.

| acquisition #        | acquisition # | acquisition #              | acquisition # | acquisition # |

|----------------------|---------------|----------------------------|---------------|---------------|

| acquisition<br>count |               |                            |               |               |

|                      |               | buffer length = n *acquisi | tion count -  |               |

In the transient mode with pre storage, the V205 memory is used as a circular buffer of programmable length. The V205 is "armed" by the user, and the control logic continuously fills the circular buffer with fresh data samples in anticipation of the trigger signal. When the trigger signal is received, the final "acquisition count" number of samples are stored in memory, and acquisition is automatically terminated.

To select pre-trigger storage of data in transient mode, the Arm register must be written to as the last action of configuring the board. This will cause the board to start acquiring data. If the Arm register is not written, pre-trigger storage will not occur.

The basic idea: When using pre-trigger storage, acquisition count and memory buffer size may be independently set. Data stored in the memory buffer will be divided into two sections: data acquired *before* the application of the trigger, and data acquired *after* the application of the trigger.

| pre-trigger data | post trigger data |

|------------------|-------------------|

|                  | acquisition count |

| buffer length    |                   |

## Cascading Multiple Boards

The V205 provides simultaneous sampling not only on all channels on one board, but also on all channels across multiple boards. The V205 PLL clock circuitry allows multiple board systems to have simultaneous triggering (± 0 samples) and less than 1.5 ns board to board sampling skew.

In order to achieve multiple board synchronization, one board is designated as the "Master" and provides clock and trigger signals to the other ("Slave") boards in the group. As with single boards, either internal or external clock and trigger signals may be used with multiple board configurations. In the case of external clock and/or trigger, the user supplies the external signal(s) to the master, which in turn distributes the clock and trigger to the slaves. Master/slave status must be programmed in the Control register. The P4 connector on the front panel of the V205 provides access to all signals necessary for multiple card synchronization. Details of the P4 pinout are given in appendix. The term "Master" in this context should not be confused with VXIbus bus mastership.

Important note: All boards to be synchronized must be located in the same VXIbus chassis in order to avoid violation of signal timing requirements.

## Related products

## **Getting Started**

To set up and use your V205 VXIbus module, you will need most or all of the following:

- The V205 16-bit ADC module and this User Manual

- Your VXIbus system with its Resource Manager and high-level test and/or application software

# **Unpacking the V205**

The V205 comes in an anti-static bag to avoid electrostatic damage. Electrostatic discharge to the module can damage components on it. Please take the following precautions when unpacking the module:

- Ground yourself with a grounding strap or by touching a grounded object.

- Touch the anti-static package to a metal part of your VXIbus chassis before removing the module from the package.

- Remove the module from the package and inspect the module for damage.

- Do not install the module into the VXIbus chassis until you are satisfied that the module exhibits no obvious mechanical damage and is configured to conform to the desiring operating environment. The next chapter describes installation and configuration.

# **Chapter 2: Installation and Configuration**

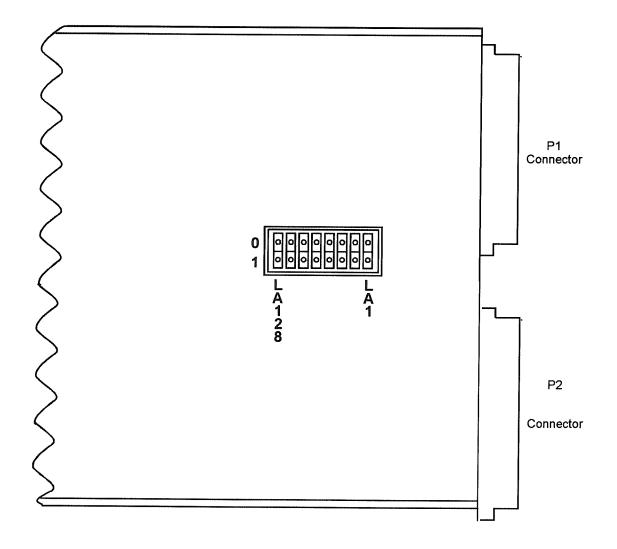

## **Setting the Logical Address Switches**

A VXI system can have as many as 255 devices, with each having a unique number in the range from 0 to 254. Eight bits represent the number, which is the Logical Address of the device.

VXIbus defines two concepts of addressing: "static" and "dynamic." All VXIbus devices *must* allow static addressing, in which the address is determined by the setting of a switch register. VXIbus devices may, but are not required to, support dynamic addressing. In dynamic addressing, the Logical Address is stored in a software-addressable register.

Before installing the V205 in the VXIbus chassis, you must set the switch register to an appropriate value. If you wish to employ static addressing you must make sure you set the switch register to a unique value other than 0 or 255. It is a good idea to note module addresses in an accessible log, because if you replace a module, it is very important that the new module have the same address as the replaced one.

If your system employs dynamic addressing, which delegates the task of assigning device addresses to the Resource Manager software, then make sure the address switch is set to 255 (all "1"s).

Note: To set a Logical Address bit to "1" depress the bottom segment of the switch.

Figure 2-1: V205 Logical Address Switch Locations

## **Module Insertion**

Before inserting your VXIbus module into the chassis, make sure that the chassis is plugged into electrical power but *not turned on*. The power cord provides a ground connection for the mainframe and protects the equipment and you from electrical harm.

In a VXI system, the Bus Grant and IACK signals are received and transmitted by each of the modules. These signals must be jumpered around any vacant slots in the mainframe. Most current mainframes, including our V194 and V195, contain jumperless backplanes, where the Bus Grant and IACK signals are automatically jumpered when a slot is empty.

If your mainframe does not contain a jumperless backplane, you must position certain jumpers correctly on the chassis backplane to assure that the V205 acknowledges interrupts properly. Remove the Interrupt Acknowledge (IACK) jumper from the slot selected for the V205 and install daisy-chain jumpers in any empty slots between the V205 and the Slot 0 Controller.

You can now insert the V205 into the chassis. Slowly push it in until its plug connectors are resting against the backplane connectors. Then, using evenly distributed pressure, press the module straight in until it seats in the slot and the module front panel is even with the chassis front panel. Tighten the top and bottom screws. You may now safely apply power to the V205.

## **Module Configuration**

## Setting the VXI Logical Address

You, or your software, must perform two types of module configuration. The first has to do with VXIbus-related items and involves communication with V205 configuration registers. The second deals with setting parameters related to module operation and involves communication with V205 operational registers.

VXIbus-related configuration includes setting the logical address, specifying the amount of memory space required, specifying where in memory the V205 registers and memory blocks are located, and setting interrupt levels.

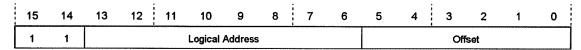

VXIbus devices occupy system memory space. The configuration registers for each VXIbus device have 64 bytes of memory space in the upper 16 Kbytes of the 64-kbyte A16 memory space. Whether you set the 8-bit Logical Address statically in the switch register or dynamically in the Logical Address register, those eight bits determines the base address of the 64-byte block of memory as follows:

| 15 | 14 | 13 | 12 | 11 | 10       | 9      | 8 | 7 | 6 | 5 | 4 | 3   | 2   | 1 | 0 |

|----|----|----|----|----|----------|--------|---|---|---|---|---|-----|-----|---|---|

| 1  | 1  |    |    | ı  | ogical . | Addres | s |   |   |   |   | Off | set |   |   |

Each 64-byte block contains several registers that supply information about the module, such as the manufacturer, the module identifier (i.e., "205h"), its class (register-based or message-based), serial number, and the amount of memory space it requires.

In addition to A16 addressing, a VXIbus device can also support A24 or A32 addressing. The V205 supports both A16 and A32 addressing.

Most operational registers are all in A32 space. To access them, one must first write a proper offset value to the Offset register in A16 space. One operational register for configuring VXI trigger functions is lo-

cated in the A16 address space.

Refer to Chapter 3 for details relating to the configuration and operational registers.

# Chapter 3: Configuration and Operational Registers

## **Address Space**

VXIbus uses the VMEbus protocol for data transfer and therefore supports 32-bit addressing to access I/O slave devices. 32-bit addressing provides direct access to memory space of four Gigabytes.

Slave devices such as VXIbus data acquisition modules exist for a variety of purposes and can be simple or very complex. Communication between host and slave can require access to several registers in one device or access to many Mbytes of memory in another. ("Devices" and "modules" are terms often used interchangeably. The distinction is that more than one VXIbus device *can* reside in a VXIbus module. However, there is generally one device per module.)

To minimize the amount of address-decoding hardware needed, simpler slave devices use addressing modes that fully decode only 16 or 24 address lines rather than 32. Therefore, there are three defined addressing modes... A16, A24 and A32... having address spaces of 64 Kbytes, 16 Mbytes and 4 Gbytes, respectively.

All VXIbus devices have registers located within 64-byte blocks in A16 address space and therefore support A16 addressing. Devices requiring no more than 64 bytes of address space need only support A16 addressing. Devices needing more than the 64 bytes to accommodate additional registers or blocks of memory *must* also support A24 or A32 addressing, but not both.

VXIbus devices that use A24 or A32 addressing modes are required to have four registers in A16 space for parameter definition. One such parameter is Required Memory, which uses four bits (m) to specify the size of the memory in A24 or A32 space required by the device. A device may not use more than one-half of the memory space, and it should not use more than one-fourth. Table 3-1 shows the relationship between the four-bit parameter, m, and the memory required by the device. Note that m = 0 defines the case for maximum usage, i.e.; half of the memory space. Required Memory is specified in bits 15 - 12 in the Device Type register at offset 02h.

| m   | l   | Require | d Men   | nory   | m   | Required Memory |        |     |        |  |  |  |

|-----|-----|---------|---------|--------|-----|-----------------|--------|-----|--------|--|--|--|

| , m | Α   | 24      |         | A32    | 111 | Α               | 24     | А   | 32     |  |  |  |

| 0   | 8   | Mbytes  | 2       | Gbytes | 8   | 32              | Kbytes | 8   | Mbytes |  |  |  |

| 1   | 4   | c c     | 1       | 66     | 9   | 16              | 46     | 4   | ££     |  |  |  |

| 2   | 2   | 66      | 51 2    | Mbytes | 10  | 8               | cc     | 2   | 66     |  |  |  |

| 3   | 1   | 44      | 25<br>6 | cc     | 11  | 4               | 66     | 1   | CL.    |  |  |  |

| 4   | 512 | Kbytes  | 12<br>8 | 66     | 12  | 2               |        | 512 | Kbytes |  |  |  |

| 5   | 256 | 66      | 64      | 66     | 13  | 1               | ££     | 256 | "      |  |  |  |

| 6   | 128 | LC      | 32      | 66     | 14  | 512             | bytes  | 128 | "      |  |  |  |

| 7   | 64  | **      | 16      | 66     | 15  | 256             | 66     | 64  |        |  |  |  |

Table 3-1: Relationship between the "m" Parameter and Required Memory

One of the four registers is the Offset register, which is needed only for devices using A24 or A32 address space. This 16-bit read/write register defines the base address of the device's A24 or A32 operational registers. The m+1 most significant bits of the Offset register provide the values of the m+1 most significant bits of the device's A24 or A32 register addresses, where m is as defined in Table 4-1 above.

# **Static and Dynamic Configuration**

A VXIbus system can have up to 255 devices. Therefore, eight bits define the device address, which is called the "Logical Address." The Logical Address can be "static" or "dynamic." A static address resides in an 8-bit switch register; a dynamic address resides in a write-only register. Setting the switch register to 255 (all "1"s) causes dynamic addressing to be enabled. Any other setting enables static addressing, in which case the value held in the switch register is the Logical Address.

With the Logical Address set to 255, a device responds to accesses at address 255 only when the MODID line is asserted as a qualifier by the Slot-0 controller. After a new Logical Address is written to the device, the device responds to the new address independent of the state of the MODID line.

For data acquisition and control applications, dynamic configuration is an important concept. A system often contains more than one module of a given type, and it can be easy, and sometimes desirable, to swap positions of two modules after removing them from the mainframe. If dynamic configuration is not employed, one must make sure that the switch register is correctly set when inserting or re-inserting a device. Dynamic configuration greatly simplifies system setup, since the software can assure that the devices are located in the desired slots. Dynamic configuration also allows a system's Resource Manager to configure memory usage optimally in a system.

## **Communication Protocol**

VXIbus allows communication over the backplane by either register-based or message-based protocols. With register-based protocol, the communication is via an 8-, 16- or 32-bit parallel path directly to I/O registers within the modules. With message-based protocol, an ASCII interpreter is included on each module, and the binary representations of ASCII characters are transmitted over the backplane. The advantage of message-based protocol is that English-like commands and responses can be used.

High-performance data acquisition and control modules are usually register-based because the data throughput is usually several orders of magnitude greater than with message-based devices. All Kinetic-Systems VXIbus devices are register-based.

## **Register Addressing**

The user assigns each device in a VXIbus system a unique number between 1 and 254. This 8-bit number, called the Logical Address, defines the base address for the VXIbus device registers located on the module. Each device has a 64-byte block of memory reserved for these registers. The memory blocks, called configuration space, are located in the upper 16 Kbytes of the 64-kbyte A16 address space.

Every device has at least three configuration registers: ID / Logical Address, Device Type, and Status / Control. Modules using A24 or A32 addressing must also have an Offset register. The rest of the 64-byte block can contain registers or memory appropriate for the operation of the specific device.

A device's Logical Address occupies bits 13 - 6 of the register address. Bits 15 and 14 of the address are both "1's," and the base address of the register block is therefore:

#### V\*40h+C000h

where V is the Logical Address of the device and C000h is the starting address of the top 16-kbyte block.

The address of a specific register is the base address plus an offset address. The offset is bits 5 - 0 of the register address and ranges from 00h to 3Eh.

The V205 also uses operational registers in A32 space; therefore, it is an "Extended" register-based device.

## **Required Configuration Registers**

The four required VXIbus registers are ID / Logical Address, Device Type, Status / Control, and Offset. You can access these registers by **D16** transfers only.

## ID Register

00h

This read-only register returns 5F29h.

Fields are Device Classification, Addressing Mode and Manufacturer ID.

Class = Extended Addressing Mode = A24

KineticSystems' Manufacturer ID = F29h (3881)

#### **Device Classification**

Bits 15 and 14

00 Memory device

01 Extended device

10 Message-based device

11 Register-based device

The V205 is an Extended device.

#### Addressing Mode

Bits 13 and 12

00 A24

01 A32

10 Reserved

11 A16

The V205 uses A32 addressing.

#### Manufacturer ID

Bits 11 through 0

KineticSystems' Manufacturer ID is 3881, which corresponds to F29h.

## Logical Address Register

00h

This write-only register holds the Logical Address. In systems using Dynamic Configuration, the system Resource Manager uses this register to set the Logical Address of the device.

| !<br>!     | 15 | 14 | 13 | 12    | 11   | 10 | 9 | 8 | 7 | 6 | 5 | 4       | 3       | 2 | 1 | 0 |

|------------|----|----|----|-------|------|----|---|---|---|---|---|---------|---------|---|---|---|

| Write-only |    |    |    | Not ( | Used |    |   |   |   |   |   | Logical | Address |   |   |   |

Logical Address

Bits 7 through 0

## Device Type Register

02h

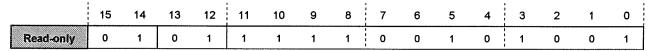

This read-only register contains the Required Memory and Model Code for the V205. It returns C205h.

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|----|---|

| Read-only | 1  | 1  | 0  | 0  | 0  | 0  | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | -0 | 1 |

Required Memory (m)

Model Code = 205h

Required Memory

Bits 15 - 12

A value of Ch is returned (m = 12 decimal), indicating that the V205 is allocated 512 Kbytes in A32 space.

Model Code

Bits 11 - 0

The model code for the V205 is 205h.

Status Register

04h

This read-only register provides binary information about the status of the V205.

| 1<br>1<br>1 | 15            | 14     | 13 | 12 | 11 | 10 | 9   | 8    | 7 | 6 | 5 | 4 | 3     | 2      | 1                  | 0             | 1 |

|-------------|---------------|--------|----|----|----|----|-----|------|---|---|---|---|-------|--------|--------------------|---------------|---|

| Read-only   | A32<br>Active | MODID* | ,  |    |    |    | Not | Used |   |   |   |   | Ready | Passed | Sysfail<br>Inhibit | Soft<br>Reset |   |

#### A32 Active

Bit 15

"1" in this field indicates that the A24 registers of the V205 can be accessed. This bit reflects the state of the Control register's A32 Enable bit.

#### **MODID\***

**Bit 14**

"1" in this field indicates that the V205 is *not* selected via the P2 MODID line. A "0" indicates that the device is selected by a high state on the P2 MODID line. The Resource Manager uses this bit to configure the V205 dynamically.

#### Ready

Bit 3

"1" in this field indicates that the registers have been successfully initialized. The V205 is ready for access.

#### Passed

#### Bit 2

"1" in this field indicates that the device self-test has passed. A "0" indicates that the V205 has failed—or is currently executing—its self-test. Since the V205 does not have a power-up self-test mechanism, this bit is always read back as a "1".

#### Sysfail Inhibit

#### Bit 1

"1" in this field indicates that the V205 is disabled from driving the SYSFAIL\* line. This bit reflects the state of the Sysfail Inhibit line in the Control register.

#### Soft Reset

#### Bit 0

"1" in this field indicates that the V205 is in a reset state. While in this state, the V205 will allow access only to its Configuration registers.

## Control Register

04h

This write-only register causes execution of specific actions by the V205.

|            | 15            | 14 | 13 | 12 1 | 10 | 9 | 8 7      | 6 | 5 | 4 3 | 3 2 | 1                  | o             |

|------------|---------------|----|----|------|----|---|----------|---|---|-----|-----|--------------------|---------------|

| Write-only | A32<br>Enable |    |    |      |    |   | Not Used |   |   |     |     | Sysfail<br>Inhibit | Soft<br>Reset |

#### A32 Enable

#### Bit 15

Setting this bit to "1" enables access of the A32 registers of the V205.

#### Sysfail Inhibit

#### Bit 1

Setting this bit to "1" disables the V205 from driving the SYSFAIL\* line.

#### Soft Reset

#### Rit 0

Setting this bit to "1" forces the V205 into a reset state.

## Offset Register

06h

This read/write register determines and reports the device base address in A32 memory space.

| i<br>t     | 15 | 14     | 13      | 12     | 11     | 10      | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----|--------|---------|--------|--------|---------|---|---|---|---|---|---|---|---|---|---|

| Read/write |    | Base A | Address | in A32 | memory | y space |   |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## **Additional Configuration Registers**

Additional configuration registers are:

- Attribute register

- Serial Number High & Low registers

- Version Number register

- Interrupt Status register

- Interrupt Control register

- Subclass register, and

- Suffix High and Low registers.

- Trigger Mapping Register

Note that you can access these registers by **D16** transfers only.

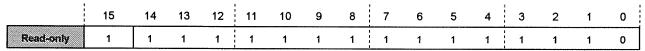

## Attribute Register

08h

This read-only register provides low-true information about the V205's interrupt handling capabilities. A read of this register returns FFFAh.

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Read-only | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

Reserved

Interrupt Interrupt Interrupt

Capability\* Handler Status

Control\* Reporting\*

#### Reserved

Bits 15 - 3

These bits are reserved for future use and return "1"s when read.

#### Interrupt Capability\*

Bit 2

"0" signifies that the V205 is capable of generating interrupts.

#### Interrupt Handler Control\*

Bit 1

"1" indicates that the V205 is *not* capable of Interrupt Handler Control.

#### Interrupt Status Reporting\*

Bit 0

"0" indicates that the V205 has Interrupt Status Reporting capability.

## Serial Number Register

OAh, OCh

The read-only Serial Number registers (high and low words) store the 32-bit hexadecimal value of the V205's decimal serial number.

|--|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4 | 3 | 2 | 1  | 0 |

|-----------|----|----|----|----|----|----|----|---|---|---|----|---|---|---|----|---|

| Read-only |    | SI | N7 |    |    | 81 | 16 |   |   | s | N5 |   |   | S | N4 |   |

High word

0Ch

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6  | 5  | 4 | 3 | 2 | 1  | 0 |

|-----------|----|----|----|----|----|----|----|---|---|----|----|---|---|---|----|---|

| Read-only |    | SI | N3 |    |    | 81 | 12 |   |   | SI | N1 |   |   | S | NO |   |

Low word

## Version Number Register

0Eh

This read-only register gives the hardware and firmware revision numbers of the module.

| !         | 15 | 14 | 13       | 12 | 11 | 10       | 9       | 8 | ; | 7 | 6       | 5        | 4 | : | 3 | 2        | 1      | 0  |   |

|-----------|----|----|----------|----|----|----------|---------|---|---|---|---------|----------|---|---|---|----------|--------|----|---|

| Read-only |    |    | e Versio | n  |    | Firmware | Revisio | n |   |   | Hardwar | e Versio | n |   | ŀ | lardware | Revisi | on | 1 |

Firmware Version

Bits 15 - 12

Firmware Revision

Bits 11 - 8

Hardware Version

Bits 7 - 4

Hardware Revision

Bits 3 - 0

Each field is a four-bit integer indicating the version or revision number.

## Interrupt Status Register

1Ah

This read-only register provides information about the state of the interrupt source within the V205.

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7 | 6 | 5 | 4         | 3       | 2 | 1 | 0 |

|-----------|----|----|----|----|----|----|---|-----|---|---|---|-----------|---------|---|---|---|

| Read-only | 0  | 0  | 0  | 0  | 0  | 0  | 0 | IRQ |   |   |   | Logical . | Address |   |   |   |

Not Used

Bits 15-9

These bits are not used and returned as zeros, but should also be written as zero.

Interrupt Request

Bit 8

A "1" read back from this bit location indicates that an interrupt is pending due to a request from the V205. This bit is latched and auto-cleared when this register is read or an interrupt acknowledge cycle is executed.

Logical Address

Bits 7 - 0

During a programmed control read operation, these bits return all "1's." During an interrupt acknowledge cycle, these bits return the V205's Logical Address.

## Interrupt Control Register

1Ch

The read/write register contains mask bits for the interrupt source, a bit for disabling interrupts and three bits that determine interrupt level. All of the bits in this register are set to "1" on the assertion of SYSRESET.

|            | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8           | 7   | 6 | 5       | 4       | 3        | 2 | 1 | 0 |

|------------|----|----|----|----|----|----|---|-------------|-----|---|---------|---------|----------|---|---|---|

| Read/write | 1  | 1  | 1  | 1  | 1  | 1  | 1 | *IRQ<br>ENA | EN* | 1 | Interru | ıpt Red | q. Level | 1 | 1 | 1 |

Not Used

Bit 15 - 9

These bits are not used and should be written as "1"'s when writing to this register.

#### Interrupt Request Enable

Bit 8

Writing a "1" to this bit *prevents* the V205 from generating an interrupt request. Writing a "0" enables the interrupt source to generate an interrupt request.

#### Interrupt Enable

Bit 7

Writing a "1" to this bit disables interrupt generation. Writing a "0" enables interrupt generation.

#### Interrupt Request Level

Bits 5 - 3

These bits determine the interrupt request level.

| 5 | Bits<br>4 | 3 | Interrupt Request Level |

|---|-----------|---|-------------------------|

| 0 | 0         | 0 | IRQ7                    |

| 0 | 0         | 1 | IRQ6                    |

| 0 | 1         | 0 | IRQ5                    |

| 0 | 1         | 1 | IRQ4                    |

| 1 | 0         | 0 | IRQ3                    |

| 1 | 0         | 1 | IRQ2                    |

| 1 | 1         | 0 | IRQ1                    |

| 1 | 1         | 1 | Disconnected            |

Table 3-2: Interrupt Request Levels

#### **Not Used**

Bits 2 - 0

Bits 2 - 0 are not used and return "1"s when read.

Note: Prior to configuring the interrupt selection and enables in this register, the interrupts MUST be enabled prior to configuration through the Interrupt Configuration Register in A32 address space.

## Subclass Register

1Eh

This read-only register provides information about the Subclass of the VXIbus device.

Extended Device

**Extended Register-based Device**

Bit 15 indicates that the V205 is a VXIbus-defined Extended Device.

Bits 14 through 0 indicate that the V205 is an Extended Register-based Device.

## Suffix Register

20h, 22h

00L

The Suffix read-only register (high and low words) holds the ASCII codes for the four characters of the V205's suffix. The suffix defines the optional characteristics of the module.

|           |    |    |    |    |    |    |   |   |   |   |   |   |   |   | 201 | n |   |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|-----|---|---|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 | 1 |

| Read-only | 0  | 1  | 0  | 0  | 1  | 1  | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | х   | ж |   |

ASCII code for A, B, or C = 41h, 42h or 43h (1st character)

ASCII code for A = 41h (2<sup>nd</sup> character)

|           |    |    |    |    |    |    |   |   |   |   |   |   |   |   | 221 |   |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|-----|---|

| !<br>!    | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

| Read-only | 0  | 0  | 1  | 1  | 0  | 0  | х | х | 0 | 0 | 1 | 1 | 0 | 0 | х   | х |

ASCII code for 1 = 31h (3<sup>rd</sup> character)

ASCII code for 1, 2, etc. = 31h, 32h, etc. (4th character)

The suffix options for the V205 are:

1st character:

Specifies the number of ADC Channels

"A" indicates a module with 8 channels.

"B" indicates a module with 16 channels.

"C" indicates a module with 32 channels.

2<sup>nd</sup> character:

"A" for all options.

3<sup>rd</sup> character:

"1" for all options.

4<sup>th</sup> character:

Revision level

The number, "1," "2," etc., gives the module revision level.

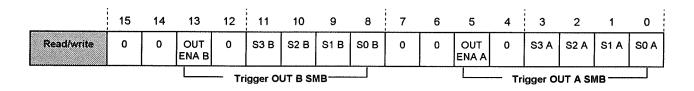

## Trigger Mapping Register

36h

The Trigger Mapping Register is a write/read register used to control the configuration of the Front Panel Mounted Trigger OUT B and Trigger OUT A SMB's. Under software control, these two SMB's can be mapped as outputs from the VXI trigger lines. The triggers can be mapped to either the TTL or ECL trigger lines. The following shows a bit layout for the Trigger Mapping Register.

Not Used

Bits 15-14

These bits are not used and read as "0"s.

#### Output Enable B

#### **Bit 13**

This write/read bit is used to enable the Front Panel Trigger OUT B SMB as an output. The SMB signal is asserted by the V205 when the trigger line configured by bits 11 through 8 is asserted. The SMB is configured as an output of the V205 when this bit is set to a "1" and disabled from being an output when set to "0".

#### Not Used

#### Bit 12

This bit is not used and should be written to a "0".

#### Select 3B through Select 0B

#### Bits 11-8

These write/read bits are used to configure the VXI Trigger Line mapping when enabled as an output from the V205. The binary combination of these bits determine the mapping as shown in the following table.

|    | Bi | ts |   | Mapped Trigger Line |

|----|----|----|---|---------------------|

| 11 | 10 | 9  | 8 |                     |

| 0  | 0  | 0  | 0 | TTL Trigger Line 0  |

| 0  | 0  | 0  | 1 | TTL Trigger Line 1  |

| 0  | 0  | 1  | 0 | TTL Trigger Line 2  |

| 0  | 0  | 1  | 1 | TTL Trigger Line 3  |

| 0  | 1  | 0  | 0 | TTL Trigger Line 4  |

| 0  | 1  | 0  | 1 | TTL Trigger Line 5  |

| 0  | 1  | 1  | 0 | TTL Trigger Line 6  |

| 0  | 1  | 1  | 1 | TTL Trigger Line 7  |

| 1  | 0  | 0  | 0 | ECL Trigger Line 0  |

| 1  | 0  | 0  | 1 | ECL Trigger Line 1  |

Table 3-3: V205 Bits 11-8 Mapped Trigger Line

#### Not Used

#### Bits 7-6

These bits are not used and read as "0"s.

#### Output Enable A

#### Bit 5

This write/read bit is used to enable the Front Panel Trigger I/O A SMB as an output. The SMB signal is asserted by the V205 when the trigger line configured by bits 3 through 0 is asserted. The SMB is configured as an output of the V205 when this bit is set to a "1" and disabled from being an output when set to "0".

#### Not Used

#### Bit 4

This bit is not used and should be written to a "0".

#### Select 3A through Select 0A

#### Bits 3-0

These write/read bits are used to configure the VXI Trigger Line mapping when enabled as an output from the V205. The binary combination of these bits determine the mapping as shown in the following:

|   | В | ts |   | Mapped Trigger Line |

|---|---|----|---|---------------------|

| 3 | 2 | 1  | 0 |                     |

| 0 | 0 | 0  | 0 | TTL Trigger Line 0  |

| 0 | 0 | 0  | 1 | TTL Trigger Line 1  |

| 0 | 0 | 1  | 0 | TTL Trigger Line 2  |

| 0 | 0 | 1  | 1 | TTL Trigger Line 3  |

| 0 | 1 | 0  | 0 | TTL Trigger Line 4  |

| 0 | 1 | 0  | 1 | TTL Trigger Line 5  |

| 0 | 1 | 1  | 0 | TTL Trigger Line 6  |

| 0 | 1 | 1  | 1 | TTL Trigger Line 7  |

| 1 | 0 | 0  | 0 | ECL Trigger Line 0  |

| 1 | 0 | 0  | 1 | ECL Trigger Line 1  |

Table 3-4: V205 3-0 Mapped Trigger Line Bits

# **Operational Registers**

The following sections describe the set of Operational Registers on the V205. This set of registers is located in A32 address space and must be accessed by D32 transfers only. Accessing these registers by any other data word size than D32 will result in erroneous behavior.

The following table is a summary of registers available on the V205. Additional information on each register is available under its individual description.

| Register                         | Offset        | Access Type          |

|----------------------------------|---------------|----------------------|

| Status Register                  | Base + 00004h | Read-Only            |

| Interrupt Mask Register          | Base + 00008h | Read/Write           |

| Control Register                 | Base + 0000Ch | Read/Write           |

| Channel Count Register           | Base + 00010h | Read/Write           |

| Buffer Length Register           | Base + 00014h | Read/Write           |

| Acquisition Count Register       | Base + 00018h | Read/Write           |

| Decimation                       | Base + 0001Ch | Read/Write           |

| ADC Clock Register               | Base + 00024h | Write-Only           |

| Arm Register                     | Base + 0002Ch | Write-Only           |

| ADC Reset Register               | Base + 00030h | Write-Only           |

| Buffer Reset Register            | Base + 00034h | Write-Only           |

| Board Reset Register             | Base + 00038h | Write-Only           |

| Interrupt Configuration Register | Base + 1008Ch | Write-Only           |

| ADC Data Register                | Base + 40000h | Read-Only/Write-Only |

## Status Register (SR)

00004h

The Status Register contains information about the state of the V205, including the status of events, which may cause VXIbus interrupts, if the appropriate bits of the Interrupt Mask register (IMR) are set. The Status Register should be used to determine the interrupt status of the V205. Several other indicators exist in this register for status and error reporting.

|           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22          | 21          | 20                  | 19  | 18 | 17 | 16 |

|-----------|----|----|----|----|----|----|----|----|----|-------------|-------------|---------------------|-----|----|----|----|

|           | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0           | 0           | 0                   | 0   | 0  | 0  | 0  |

| Read-Only | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6           | 5           | 4                   | 3   | 2  | 1  | 0  |

|           | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | CLK<br>BUSY | SYNC<br>ERR | DIAG<br>FIFO<br>EMP | IRQ | 0  | 0  | 0  |

Not Used

Bit 31-7

These bits are not used and should be ignored.

#### **CLK BUSY**

Bit 6

This bit indicates that the programmable clock is busy. Whenever accessing the ADC CLOCK registers, this bit is monitored between successive writes until it is low.

SYNC ERR

Bit 5

This bit indicates that a synchronization error has occurred among the ADCs. This indicates that one or more ADCs on this board is out of sync with respect to the oversampling decimation of other ADCs in the system. In order to correct this, the user should resynchronize the converters by means of a write to the ADC Reset register.

DIAG FIFO EMPTY

Bit 4

This bit indicates that the Diagnostics FIFO is empty and is ready for more data.

*IRQ*

Bit 3

This bit indicates that the V205 is asserting a VXIbus interrupt from any source.

Not Used

Bits 2-0

These bits are not used and read as "0".

## Interrupt Mask Register (IMR)

00008h

Read/Write

The Interrupt Mask register is used to enable and disable VXIbus interrupts. The status of interrupts (asserted/not asserted) may be read in the corresponding bits of the status register, but no interrupt will occur unless the appropriate mask bit is set in this register.

|            | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17                | 16             |

|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------------------|----------------|

|            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0                 | 0              |

| Write/Read | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1                 | ــــــا<br>ا ه |

|            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | ADC<br>IRQ<br>ENA | 0              |

#### ADC IRQ Enable

Bit 1

This bit enables the ADC control unit controller to generate VXIbus interrupts. Setting this bit to a "1" enables the interrupt source and a "0" disable the source.

**Not Used**

Bit 0

This bit is not used and read as a "0".

#### Control Register (CR)

0000Ch

The Control Register is a write/read register that is used to control the overall configuration of the V205. The following is the bit layout for the Control Register.

|            | 31 | 30  | 29          | 28 | 27         | 26 | 25 | 24 | 23                 | 22          | 21 | 20 | 19 | 18          | 17         | 16          |

|------------|----|-----|-------------|----|------------|----|----|----|--------------------|-------------|----|----|----|-------------|------------|-------------|

|            | 0  | 0   | 0           | 0  | 0          | 0  | 0  | 0  | 0                  | 0           | 0  | 0  | 0  | 0           | 0          | 0           |

| Write/Read | 15 | 14  | 13          | 12 | 11         | 10 | 9  | 8  | 7                  | 6           | 5  | 4  | 3  | 2           | 1          | ا ه         |

|            | 0  | ENA | INT<br>TRIG | 1  | AE<br>OSAM |    | 0  | 0  | ADC<br>CLK<br>TERM | ADC<br>MSTR | 0  | 0  | 0  | DIAG<br>ENA | CLK<br>SEL | TRIG<br>SEL |

Not Used

Bits 31-15

These bits are not used and should be ignored.

Enable

**Bit 14**

This bit is used to enable the ADC's to acquire data and move it into the storage buffer. After this bit is set to a "1" and external triggering is selected, the acquisition will start following the next rising edge of the external trigger input. After this bit is set to a "1" and internal triggering is selected, acquisition will start with the first valid data after the trigger bit, bit 13, has been set. This bit should be cleared to a "0" disable acquisition.

Internal Trigger

**Bit 13**

This bit is the internal trigger signal that can be used to initiate a transient capture. The Enable bit, bit 14 of this register, must have been previously set to a "1", and Trigger Select, bit 0 of this register, must be set to internal trigger, in order for this bit to be effective. This bit is automatically cleared after acquisition is started.

Reserved

Bit 12

This bit is reserved and MUST be set to a "1" in order for the V205 to properly function.

ADC Oversampling Ratio

Bit 11-10

These bits select the oversampling ratio of the converters. All converters on the board are programmed to the same ratio. The valid selections for the oversampling ratios are 8x, 4x, and 2x. To determine the output rate for a given channel, one must divide the oversample clock to the ADC's by the oversampling

ratio. For example, an ADC running with a 10 MHz oversample clock, the output rate at 8x oversample is 1.25 MHz, at 4x is 2.5 MHz, and at 2x is 5 MHz. The following table shows the various binary combinations of these bits that yield the indicated oversampling ratios.

| E  | lits | Observation Prof.  |

|----|------|--------------------|

| 11 | 10   | Oversampling Ratio |

| 0  | 0    | 8x Oversampling    |

| 0  | 1    | 4x Oversampling    |

| 1  | 0    | 2x Oversampling    |

| 1  | 1    | Reserved           |

Reserved

Bit 9-8

These bits are reserved and MUST be set to "0".

#### ADC Clock Termination

Bit 7

This bit is used to connect the resistive termination to the P4 ADC\_CLK line. This bit is only useful in configurations using multiple V205's that are to run off the same sample clock signal. This bit must be set to a "1" on the End Slave board only, and only in multiple board configurations. The End Slave refers to the last physical V205 in a multiple module configuration.

#### ADC Sampling Master Enable

Bit 6

This bit is used to select a board as a Sampling Master or Slave, when operating in a multiple V205 board acquisition cluster. In the cluster, only one board can be set as a Master. The Master board sends the ADC\_CLK signal (pin 1 and 2 on the P4 connector) and the Trigger signal (pin 10 on the P4 connector) to all slaves. The ADC\_CLK signal is in PECL format. Slaves receive the ADC\_CLK on the P4 connector pin 1 and 2 and the Trigger signals on pin 10. The Master must be located at one physical end of the P4 Local Bus cable. When using a single V205, the board must be configured as Sampling Master. This bit is set to a "1" to configure the V205 as a Sampling Master and reset to a "0" to configure the V205 as a Sampling Slave.

Reserved

Bit 5-3

These bits are reserved and MUST be set to "0".

#### Diagnostic Mode Enable

Bit 2

This bit is used to enable the Diagnostic mode. The Diagnostic Mode is enabled by setting this bit to a "1" and disable by resetting this bit to a "0". In this mode, VXIbus data can be written to the buffer and verified for consistency. Once the mode is cleared, the data can be read back from the buffer. Details of the use of diagnostic mode are given in the section of this manual entitled *Using Diagnostic Mode*.

#### Sampling Clock Select

Bit 1

This bit selects between internal and external sampling clocks for the ADC. Resetting this bit to a "0" selects the internal sample clock and setting this bit to a "1" selects external sample clock. Note that when using the external sample clock, that the clock input to the V205 must be twice that of the actual desired

sample rate.

#### Trigger Select

#### Bit 0

This bit determines if the external ADC Trigger is used to start an acquisition. When using an external trigger, triggering occurs following the rising edge of the trigger signal. The signal must remain high for at least one complete acquisition (clock) cycle. External trigger events are enabled by setting this bit to a "1" and disabled by setting the bit to a "0".

# **Channel Count Register**

00010h

This write/read register determines the number of active channels on the board to participate in conversions. Only the samples coming from the active channels are stored in the buffer and moved to the output interface. A value (N-1) written in this register will activate channels 1 to N. N must be an even number. The valid range of numbers that may be programmed to this register is 1 to 31.

|            | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19  | 18       | 17   | 16 |

|------------|----|----|----|----|----|----|----|----|----|----|----|----|-----|----------|------|----|

|            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0        | 0    | 0  |

| Write/Read | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3   | 2        | 1    | o  |

|            | o  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |    | Cha | innel Co | ount |    |

#### Not Used

Bits 31-5

These bits are not used and should be ignored.

#### Channel Count

Bits 4-0

These write/read bits are used to configure the number of active channels on a V205. The actual value loaded into this register is one less than the desired parameter. The legal values for data loaded into this register range from 0 to 31.

#### Buffer Length Register

00014h

The Buffer Length is a write/read register used to specify the total number of sample pairs acquired for all active channels before acquisition terminates. When operating in transient mode without pre-trigger storage, the buffer length selected must be an integral multiple of the Acquisition Count. The value written to this register must be one less than the required buffer length. If the ADC interrupt is enabled, a VXIbus

interrupt will occur when the programmed length is reached. The valid range of numbers that may be programmed to this register is 0 to 524287. The maximum value is equivalent to the maximum buffer capacity of 1Msample.

The user must perform a Buffer Reset (by writing to the Buffer Reset register) after loading the Buffer Length, Acquisition Count, Decimation and Frame Count registers in order for the new values to take effect.

|            | 31 | 30 | 29     | 28     | 27      | 26    | 25 | 24 | 23 | 22 | 21    | 20      | 19         | 18    | 17                  | 16 |

|------------|----|----|--------|--------|---------|-------|----|----|----|----|-------|---------|------------|-------|---------------------|----|

|            | 0  | 0  | 0      | 0      | 0       | 0     | 0  | 0  | 0  | 0  | 0     | 0       | 0          |       | er Leng<br>hrough 1 |    |

| Write/Read | 15 | 14 | 13     | 12     | 11      | 10    | 9  | 8  | 7  | 6  | 5     | 4       | <u> </u> 3 | 2     | 1                   | 0  |

|            |    |    | Buffer | Length | 15 thro | ugh 8 |    |    |    |    | Buffe | r Lengi | h 7 thro   | ugh 0 |                     |    |

#### Not Used

Bits 31-19

These bits are not used and should be ignored.

#### **Buffer Length**

Bits 18-0

These write/read bits are used to specify the total number of sample <u>pairs</u> acquired for all active channels before the operation terminates. The value in this register can range from 0 to 524287.

# **Acquisition Count Register**

00018h

The Acquisition Count Register is a write/read register that determines the number of 32-bit words to be stored in the buffer following each application of a trigger when operating in transient mode with no pre-trigger storage. When operating in transient mode with pre-trigger storage, it determines the number of 32-bit words acquired after the (single) occurrence of the trigger. Two samples are stored in each 32-bit buffer word. The value is programmed as one less than the required length. The relationship between samples acquired on each channel, and the value programmed to this register is therefore as follows:

$$AC = (S \times C/2) - 1,$$

where

AC = Value programmed to Acquisition Count register

S = Number of samples to be acquired on each channel

C = Number of active channels selected in Channel Count register

The valid range of numbers that may be programmed to this register is 0 to 524287. The user must perform a Buffer Reset (by writing to the Buffer Reset register) after loading the Buffer Length, Acquisition

Count, Decimation and Frame Count register is order for the new values to take effect.

| 000000000000000000000000000000000000000 | 31                             | 30 | 29 | 28 | 27 | 26                            | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17                    | 16 |

|-----------------------------------------|--------------------------------|----|----|----|----|-------------------------------|----|----|----|----|----|----|----|----|-----------------------|----|

|                                         | 0                              | 0  | 0  | 0  | 0  | 0                             | 0  | 0  | 0  | 0  | 0  | 0  | 0  |    | sition Co<br>nrough 1 |    |

| Write/Read                              | 15                             | 14 | 13 | 12 | 11 | 10                            | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1                     | 0  |

|                                         | Acquisition Count 15 through 8 |    |    |    |    | Acquisition Count 7 through 0 |    |    |    |    |    |    |    |    |                       |    |

Not Used

Bits 31-19

These bits are not used and should be ignored.

#### **Acquisition Count**

Bits 18-0

These write/read bits are used to specify the number of 32-bit data words to be stored upon each application of a trigger.

#### **Decimation Count Register**

0001Ch

This write/read register programs the eight-bit decimation count. The real output rate is the ADC output rate divided by the decimation factor. The decimation factor is one greater than the value written to this register. Therefore, setting this register to zero disables decimation, while writing one to this register will result in decimation by a factor of 2. This feature enables the output rate to be reduced, allowing operation of the V205 with an effective sample output rate below the converter minimum for the selected oversampling ratio. However, the user is cautioned that decimating the output in this way interacts with the oversampling technology of the converters, and may cause aliasing of any signals that are in the ADC's bandwidth. The valid range of numbers that may be programmed to this register is 0 to 255, corresponding to decimation factors of 1 to 256.

The user must perform a Buffer Reset (by writing to the Buffer Reset register) after loading the Buffer Length, Acquisition Count and Decimation register in order for the new values to take effect.

|            | 31 | 30 | 29       | 28 | 27       | 26 | 25       | 24       | 23 | 22 | 21 | 20       | 19      | 18 | 17 | 16 |

|------------|----|----|----------|----|----------|----|----------|----------|----|----|----|----------|---------|----|----|----|

|            | 0  | 0  | 0        | 0  | 0        | 0  | 0        | 0        | 0  | 0  | 0  | 0        | 0       | 0  | 0  | 0  |

| Write/Read |    |    | <u> </u> |    | <u>i</u> | L. | <u> </u> | <u> </u> |    |    |    |          |         |    |    |    |

|            | 15 | 14 | 13       | 12 | 11       | 10 | 9        | 8        | 7  | 6  | 5  | 4        | 3       | 2  | 1  | 0  |

|            | 0  | 0  | 0        | 0  | 0        | o  | o        | 0        |    |    | Ε  | ecimatio | on Cour | ıt |    |    |

#### Not Used

Bits 31-8

These bits are not used and should be ignored.

#### **Decimation Count**

Bits 7-0

These write/read bits are used to specify output decimation factor. The value loaded into this register is actually 1 less than the desired factor. Loading a value of zero disables decimation.

# ADC Clock Frequency Register

00024h

This write/read register allows the user to program the internal sampling (conversion) frequency. This is done by writing a 22-bit programming word to the on-board programmable oscillator. Data is written serially to the oscillator, least significant bit first. One write to the register must occur for each bit of data to be written to the oscillator, with the data to be programmed in bit 0. Note that the frequency programmed must be twice the oversampling frequency, rather than the output rate. See details for programming the oscillator in the section entitled Programming the Internal Clock Generator.

# Arm Register

0002Ch

This write-only register is used to initiate pre-storage of data when the V205 is used in transient mode with pre-trigger storage. Any data pattern may be written to this register to place the V205 in an armed state. See details on using pre-trigger storage in section entitled *Modes of Operation*.

# ADC Reset Register

00030h

A write to this register synchronizes all onboard ADC's. It does not alter memory contents or the values of control registers. The data written to the register is unimportant. The register should be written to after the board is configured and before acquisition is started.

# Buffer Reset Register

00034h

A write to this register resets the ADC buffer memory pointers and validates configuration settings. It does not alter memory contents or the values of control registers. The value written to the register is un-

important. This register must be written to after configuring the ADC section and before enabling acquisition in order for the buffer memory to be correctly initialized.

### **Board Reset Register**

00038h

A write to this register masks all interrupts, resets all control register bits to their power-up defaults (zero) and resets all on-board memory. The data written to the register is unimportant. The register should only be written to in order to perform a complete reset of the board prior to changing the board configuration.

# Interrupt Configuration Register

1008Ch

This write-only register MUST be written with data set to 10 (0Ah) in order for the V205 to generate VXIbus interrupts. This write operation is used to enable hardware specific interrupt circuitry on the V205.

ADC Data 40000

This section of the V205 VXIbus memory map is used to read data from the ADC memory over the VXIbus. The VXIbus ADC Data area is 40000h bytes (256KB) in size. Therefore, the ADC Data locations can be accessed from address offset 40000h to 7FFFFh. The ADC memory buffers are strictly read only. The same area of the memory map allows test pattern data to be written to the diagnostic FIFO, which is strictly write only. See the section entitled *Using Diagnostic Mode* for details on using the built-in diagnostics.

The data is organized as one sample in each 16-bit word, with "big endian" ordering. i.e.; odd channels occupy the most significant 16 bits and even channels occupy the least significant 16 bits of a 32-bit longword, where channels are numbered from 1 to 32.

The data area appears to the user as FIFO type memory. In other words, random access to samples in the memory is not available. Data access is always sequential regardless of the address used for read or write, as long as the address used falls within the ADC Data area.

Each time a data word is read from the buffer, the data is removed from memory and buffer pointers are modified. The user must be careful to read the exact number of 32-bit words corresponding to the programmed buffer length, otherwise buffer overflow or underflow will occur.

The user should perform a reset of the memory (ADC Reset and Buffer Reset) after programming the ADC configuration and before enabling acquisition. This is necessary to ensure that the buffer pointers are correctly aligned prior to buffer access by the ADC circuits and that the ADCs are synchronized.

Addresses presented by the bus master when reading data may be either incremental of repetitive (i.e.; always the same address). Provided the addresses fall within the ADC Data area, consecutive data will be read from the board regardless of the addressing mode. This allows for standard addressing and block transfers with devices that either increment addresses or repetitively present the same address.

#### Using Diagnostic Mode

The V205 has built in digital diagnostic circuitry that allows the user to test all functionality of the board with the exception of the ADCs. This is accomplished by feeding the V205 with simulated ADC data from an on-board 4 Kword FIFO memory.

The diagnostic mode is used by first configuring the V205 registers and then setting the DIAG ENABLE bit, bit 2, of the Control Register. Data may then be written to the board in the ADC Data window in blocks not exceeding 4096 words. Between each block the board must be enabled and triggered until the Diag FIFO Empty bit, bit 4, in the Status register is set. The board can then be disabled and the next block written. Once all the data has been written, the DIAG ENABLE bit can then be reset, and the data written to the board can then be read back.

# Chapter 4: Programming the Internal Clock Generator

#### Introduction

The frequency of the V205 internal sampling clock is controlled by programming the programmable oscillator through the Clock Frequency register of the VXIbus memory map. The device is programmed not in engineering units, but by means of a complex programming word whose construction is described below; a series of control words must also be written to the device. Data is transferred to the device serially; it is necessary to write the data to the V205 ADC Clock register one bit at a time; bit 0 of the register is the relevant bit. Thus, the programming sequence should normally be done by repeatedly writing each control or programming word to the ADC Clock register, shifting the data right by one bit after each write, until all bits of the word have been written.

#### **Programming Summary**

The programmable oscillator contains two registers, the Control Register and the Programming Word Register. The programming sequence is as follows:

- 1. Write to Control Register to configure device and prepare the device to receive the Programming Word.

- 2. Write Programming Word.

- 3. Write to Control Register to load Programming Word data into device.

- 4. Wait at least 5mS for device Voltage Controlled Oscillator (VCO) frequency to stabilize.

- 5. Write to Control Register to enable device output of new frequency.