Digital Signal Processor

INSTRUCTION MANUAL

March 14, 2001

(C) 1994, 1996, 1998, 2000, 2001 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

## Contents

| Features                                 | 1        |

|------------------------------------------|----------|

| General Description                      |          |

| Specifications                           | 9        |

| Cross-Development Software and Utilities |          |

| Ordering Information                     | 3        |

| UNPACKING AND INSTALLATION               |          |

| Module Insertion                         | 4        |

|                                          |          |

| FRONT PANEL INFORMATION                  | 4        |

| LEDs                                     | 4        |

| Switches                                 | 5        |

| Connectors                               | 5        |

| STRAP OPTIONS AND SWITCHES               | 5        |

|                                          |          |

| Logical Address Switches                 | 5        |

| Bus Request Level Straps                 | . 6      |

| DSP Reset Vector Address Straps          | . 7      |

| Front-Panel Reset Strap                  | . 8      |

| PROGRAMMING INFORMATION                  | Q        |

| VMEbus/VXIbus Addressing                 |          |

| VXIbus Configuration Registers           | . 0      |

| ID/Logical Address Register              |          |

| Device Type Register                     | . 9      |

| Device Type Register                     | 10       |

| Status/Control Register                  | 10       |

| Offset Register                          | 11<br>12 |

| Attribute Register                       | 12<br>12 |

| Serial Number High Register              | 12       |

| Serial Number Low Register               | 13       |

| Version Number Register                  | 13       |

| Interrupt Status Register                | 14       |

| Interrupt Control Register               | 14       |

| Subclass Register                        | 16       |

| Suffix High Register                     | 16       |

| Suffix Low Register                      | 16       |

| VXI Operational Registers                | 17       |

| Semaphore Flags                          | 18       |

| DSP Control Register                     |          |

| Frame Interval Register                  | 20       |

| Frame Data Selection Words               | 21       |

| DRAM                                     | 21 |

|------------------------------------------|----|

| DSP Architecture                         | 22 |

| DSP Memory Map                           | 23 |

| DSP Memory Accesses                      | 25 |

| DSP Expansion Bus I/O Mapped Registers   | 26 |

| Digital Input Register                   | 27 |

| DMA Data Register                        | 28 |

| DMA Control/Status Register              | 28 |

| DMA Address Register                     | 30 |

| VXI Interrupt Source Register            | 30 |

| VXI Trigger Source Register              | 32 |

| VXI Trigger Select Register              | 32 |

| LED Display Register                     | 34 |

| SYSFAIL Register                         | 34 |

| DSP Semaphore Flags                      | 35 |

| DSP Reset Vector                         | 36 |

| DSP Self-Test                            | 36 |

| DSP Interrupts                           | 37 |

| DSP Serial Ports                         | 38 |

| DSP Timer/Counter                        | 38 |

| DSP Flags                                | 38 |

| DIGIBUS Overview                         | 39 |

| V165 DIGIBUS Option                      | 40 |

| DIGIBUS Acceptor Functions               | 40 |

| DIGIBUS Source Functions                 | 41 |

| DIGIBUS Acceptor Control Registers       | 42 |

| Read Frame Counter                       | 42 |

| Decrement Frame Counter                  | 43 |

| Read Frame Address                       | 43 |

| Enable DIGIBUS FIFO-To Buffer Transfers  | 43 |

| Disable DIGIBUS FIFO-To-Buffer Transfers | 43 |

| DIGIBUS Source Control Registers         | 44 |

| Generate DIGIBUS Byte Cell With Data     | 44 |

| Generate DIGIBUS Byte Cell Without Data  | 44 |

| Start DIGIBUS Frame                      | 44 |

|                                          | 44 |

| APPENDIX                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMMANDS       50         FILL_DSP_MEMORY_RECORD       50         READ_ADDRESS_RECORD       51         RECEIVE_DATA_RECORD       51         SELF_TEST_RECORD       52         SET_NEW_PC_RECORD       52         V165_001_TEST_RECORD       53         VERSION_RECORD       53         WRITE_ADDRESS_RECORD       53         WRITE_LED_RECORD       54 |

| POWER-ON SELF-TEST                                                                                                                                                                                                                                                                                                                                     |

| DOWNLOADING DSP CODE TO V165 RAM                                                                                                                                                                                                                                                                                                                       |

| INTERRUPT SERVICE & MULTIPLE TASKS                                                                                                                                                                                                                                                                                                                     |

| COMMAND RECORD HEADER FILE V165RCRD.H                                                                                                                                                                                                                                                                                                                  |

| V165 MEMORY MAP                                                                                                                                                                                                                                                                                                                                        |

| FIGURES                                                                                                                                                                                                                                                                                                                                                |

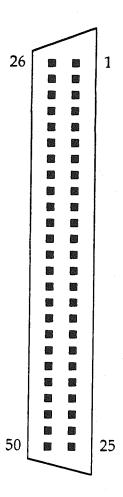

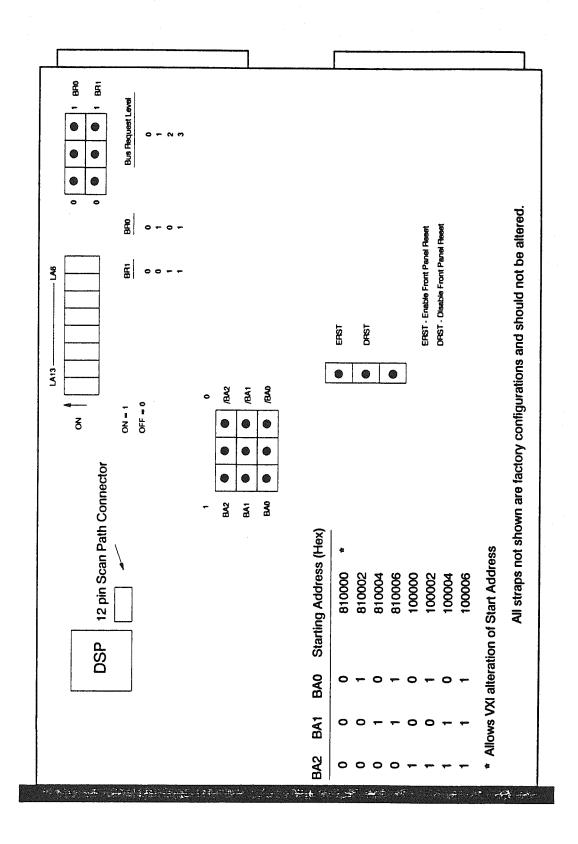

| FIGURE 1 - V165 50-Position SCSI-II Plug       47         FIGURE 2 - V165 Strap Location       48         TABLES                                                                                                                                                                                                                                       |

| TABLE 1 - Configuration Registers                                                                                                                                                                                                                                                                                                                      |

| Warranty<br>SCK:rem(WP)                                                                                                                                                                                                                                                                                                                                |

| Schematic Drawing # 292144-C-6656<br>Schematic Drawing # 232336-C-6661                                                                                                                                                                                                                                                                                 |

## **Digital Signal Processor**

## A TI-based DSP with 40 MFLOP processing power

## V165

#### **Features**

- · Performs FIR & IIR filtering

- Computes FFTs

- · Performs signal averaging

- · Executes limit checking

- Converts to engineering units

- Executes at 40 MFLOPS

- Performs 32/40-bit floating point operations

- · Includes 1 to 16 Mbyte DRAM

- · Has DMA capability

- Options for Digi-bus<sup>™</sup> input and output data paths

## **Typical Applications**

- · Wind tunnel data acquisition

- Aerospace tests

- Automotive tests

- Acoustic tests

- · General-purpose signal analysis

- · High-speed control loops

# General Description (Product specifications and descriptions subject to change without notice.) The V165 is a single-width, C-size, register-based, VXIbus module that provides realtime processing for data collected from other modules within the VXI chassis. The processing power for this module is pro-

data collected from other modules within the VXI chassis. The processing power for this module is provided by the Texas Instruments TMS320C30 ('C30) Digital Signal Processor (DSP). This DSP provides 40 MFLOP operation and its 32/40-bit floating-point arithmetic capabilities simplify the development of applications, eliminating the effects of scaling, normalization, and overflow. Implemented with low power CMOS, the 'C30 also provides 16- and 24-bit integer operations, IEEE floating-point conversion capability, a bit reversal addressing mode, eight 40-bit accumulators, two 32-bit timers, and a 64 x 32-bit instruction cache. It can implement FIR filters at 50 ns per tap and compute a 1024-point complex FFT in 3.04 ms.

The 'C30 has two blocks of 1K x 32 single-cycle, dual-access, on-chip RAM. A range of 1 to 16 Mbytes of dual-ported RAM is also provided on the module. All dual-access memory is addressable from the VXIbus as well as by the DSP. This allows application programs and data to be downloaded from the host computer and to dynamically change as conditions require. Instructions and data can arbitrarily reside in either the on-chip or off-chip memory.

Data to be manipulated by the DSP may be obtained from various sources and stored in various destinations. The data may be read or written by the V165 using Direct Memory Access (DMA). The V165 can become a master on the VXIbus and transfer data to and from other VXIbus modules within the chassis. Data may also be sent into and out of the V165 using the VXI Local Bus. For the V165-Bxyl option, this module supports a KineticSystems-developed Local Bus interface and protocol called Digi-bus<sup>TM</sup>. Digibus provides the mechanism to transfer digital data between adjacent modules at high speed without degrading the performance of the VXI system bus or introducing latency from "slow responding" VXIbus modules within the chassis.

Digi-bus data enters the V165 from the module on its right (the next higher numbered slot) and is passed to a selection mechanism on the V165 Digi-bus mezzanine board. The V165 can be programmed to accept all the incoming data or only selected subsets. The selected data is then available to the DSP through a 32 kword buffer. Circuitry on the mezzanine board allows the DSP to send data to the module on its left (the next lower numbered slot) by writing the word to a register on the mezzanine board.

The V165 can synchronize with other modules in the chassis by the use of its VXIbus triggers and interrupts. The V165 can be programmed to generate any number of simultaneous VXI triggers using the Synchronous Trigger protocol and to generate a VXI interrupt on any one of the eight VXI interrupt sources. The V165 can also be programmed to interrupt the DSP on the occurrence of a selected VXI trigger or when a VXI request is made with a write to a Generate DSP Interrupt register in A32 space on the V165. In addition, the 'C30 DSP provides two internal, 32-bit timers which can be programmed for periodic interrupts.

A 32-bit digital input register, which is directly readable by the DSP, can be written from the front-panel connector. Reduced data and results from the DSP's operation can be sent either to other VXI modules via DMA or to other Digi-bus equipped, KineticSystems VXI modules downstream from the V165. Also available at the front connector are two DSP serial ports capable of 7.69 Mbit/s operation. These ports can be used to transmit or receive serial data between this module and an external source, such as another V165 DSP module, for multiprocessor communication.

The V165 supports both static and dynamic configuration. Access to the DSP and its associated memory is through memory locations selected by the Offset Register within the VXIbus Configuration Register set. Access to these registers and memory is accomplished within A32/A16 address space using D32/D16 transfers.

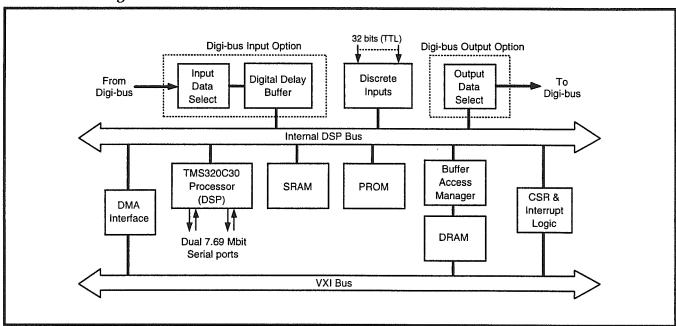

## V165 Block Diagram

## **Cross-development Software and Utilities**

The Texas Instruments TMS320 Floating-Point DSP Optimizing C -compiler, assembler, linker, emulator, and simulator are available to support application programming. This software is available for the PC/MS-DOS, VAX/VMS, and SUN-3/UNIX platforms. We also support Momentum Data Systems' QEDesign 1000 Digital Filter Design package. This package allows the user to design FIR and IIR digital filters for the V165. This software is available for the PC under Windows as well as for SUN workstations.

KineticSystems has developed a support library for the V165 DSP which offers a high-level interface to the module's hardware features. The library functions include DMA read and write, Digi-bus acceptor and source, VXI trigger interrupt service, VXI trigger and interrupt source, and timer interrupt service. Other V165 hardware features, such as the front-panel TTL inputs and the 8-bit LED status register, also have interface functions in the support library. The library distribution also includes a library header file with prototypes for all the functions, working code examples for each hardware group, and utilities which download the user's 'C30 application code to the V165 and execute it.

When used in conjunction with the Texas Instruments TMS320 Floating-Point DSP Optimizing C-Compiler package (Model AB11-DPA1), the support library can simplify the development of DSP applications for the V165. Programmers can establish the data path into and out of the V165 with DMA or Digi-bus function calls, leaving them more time to implement signal processing algorithms. While C should be the language of choice, the compiler package includes a 'C30 assembler (and other programmer's tools such as a linker and archiver) when the application must execute as quickly as possible. Both the compiler and the library support Interrupt Service Routines (ISRs) are written in C. The compiler generates entry and exit code that preserves the machine environment. The library simplifies the use of VXI and timer interrupts by setting up the interrupt vector and the interrupt masks, leaving the programmer to concentrate on the application. The distribution disk contains source and object code for VXI trigger and DSP timer ISR examples to facilitate development.

Please contact KineticSystems or your local representative for additional information about these software products.

| Item                         | Specification                                                        |

|------------------------------|----------------------------------------------------------------------|

| DSP                          |                                                                      |

| Cycle time                   | 50 ns                                                                |

| Operations per second        | 40 MFLOPS                                                            |

| Instructions per second      | 20 MIPS                                                              |

| Instruction cache            | 64 x 32                                                              |

| On-chip RAM                  | Two blocks of 1K x 32                                                |

| Timers                       | Two, 32 bits each                                                    |

| DSP Support Circuitry        |                                                                      |

| Dual-ported dynamic RAM      | 1 to 16 Mbyte, 80 ns pipelined-access                                |

| Static RAM                   | 8 kbyte to 128 kbyte, 0 wait state; optional 128 kbyte, 1 wait state |

| ROM                          | 32 kbyte to 128 kbyte, 1 wait state                                  |

| DMA                          | Supports 8, 16, and 32-bit data transfers                            |

| Digi-bus input port          | 32 kbyte x 16-bit sample buffer                                      |

| Digi-bus output port         | 16-bit samples configurable via DSP                                  |

| Discrete Digital Inputs      |                                                                      |

| Number of inputs             | 32                                                                   |

| Input signal level           | TTL                                                                  |

| Input signal logic level     | High true (0 V read by DSP as a logic "0")                           |

| Input signal termination     | Pulled up to +5 V through 4.7 kΩ resistors                           |

| Serial Ports                 |                                                                      |

| Number of ports              | 2                                                                    |

| Port direction               | Bi-directional                                                       |

| Bits per serial word         | 8, 16, 24, or 32                                                     |

| Maximum serial rate          | 7.69 Mbit/s                                                          |

| Connector Type               | 50P High Density                                                     |

| Power Requirements           |                                                                      |

| +5 V                         | 6.8 A                                                                |

| -5.2 V                       | 125 mA                                                               |

| -2 V                         | 125 mA                                                               |

| Environmental and Mechanical |                                                                      |

| Temperature range            |                                                                      |

| Operational                  | 0°C to +50°C                                                         |

| Storage                      | -25°C to +75°C                                                       |

| Relative humidity            | 0 to 85%, non-condensing to +40°C                                    |

| Cooling requirements         | 10 CFM                                                               |

| Dimensions                   | 340 mm x 233.35 mm x 30.48 mm (C-size VXIbus)                        |

| Front-panel potential        | Chassis ground                                                       |

## **Ordering Information**

Model V165-wxy1 Digital Signal Processor

w: Option cards

A = no options installed

$B = Digi-bus^{TM} Local Bus option$

x: DRAM Size

A = 1 Mbyte DRAM

B = 4 Mbyte DRAM

C = 8 Mbyte DRAM

D = 16 Mbyte DRAM

y: SRAM Size

A = 8 kbyte SRAM

B = 32 kbyte SRAM

C = 128 kbyte SRAM

D = 256 kbyte SRAM

Model V165-0001

Digi-bus Factory Upgrade

#### **Related Products**

| Model 5819-Bxyz | Cable—50S High Density to Unterminated                                    |

|-----------------|---------------------------------------------------------------------------|

| Model 5819-Dxyz | Cable—50S High Density to 50S Amphenol Ribbon                             |

| Model 5819-Fxyz | Cable—50S High Density to 50P High Density                                |

| Model 5819-Gxyz | Cable—50S High Density to 50S High Density                                |

| Model AB11-DPA1 | V165 TI Cross-development Package for MS-DOS                              |

| Model AB12-DPA1 | V165 Full Development Package for MS-DOS (Cross-development routines plus |

|                 | KineticSystems Software Support Library)                                  |

Please contact the factory for information on software packages for other operating systems.

| Model V110 | 4 to 128 Megabyte Memory                                |

|------------|---------------------------------------------------------|

| Model V207 | 16-bit, 500,000 Sample/second ADC Subsystem             |

| Model V208 | 16-bit, 100,000 Sample/second ADC Subsystem             |

| Model V285 | 8 or 16-channel, 16-bit, 500 kHz DAC/Waveform Generator |

| Model V387 | 128-channel Discrete Input/Output                       |

| Model V765 | Rack-mount Termination Panel                            |

#### UNPACKING AND INSTALLATION

The Model V165 is shipped in an anti-static bag within a styrofoam packing container. Carefully remove the module from its static-proof bag and prepare to set the various options to conform to the operating environment.

#### Module Insertion

The V165 is a C-sized, single width VXIbus module. It requires 5700 milliamperes of +5 volt power, 150 milliamperes of -5.2 volt power, 150 milliamperes of -2 volt power, and 10 cubic feet per minute of air flow to maintain stability. Except for Slot 0, it can be mounted in any unoccupied slot in a C-sized VXIbus mainframe.

CAUTION: TURN MAINFRAME POWER OFF WHEN INSERTING OR

REMOVING A VXI MODULE

WARNING: REMEMBER TO REMOVE THE INTERRUPT

ACKNOWLEDGE DAISY-CHAIN JUMPERS AND BUS GRANT-IN TO BUS GRANT-OUT JUMPERS PRIOR TO INSERTING THIS MODULE IN THE VXI BACKPLANE

To insure proper interrupt acknowledge cycles from the V165 module, the daisy-chain Interrupt Acknowledge jumper must be removed before the module is installed in a slot. Conversely, daisy-chain jumpers must be installed in any empty slot between the V165 and the Slot 0 Controller. Since the V165 may execute DMA operations to other modules within the chassis, the Bus Grant jumpers must be removed from the slot in which the V165 is installed. Ensure that the Bus Grant chain is continuous from the slot 0 controller to the V165.

#### FRONT PANEL INFORMATION

#### **LEDs**

Add Rec The Addressed Received LED is illuminated when the V165 registers are

being accessed and when the V165 acknowledges an interrupt.

Failed The Failed LED is illuminated when the V165 has failed its self-test.

Run The Run LED is illuminated as long as the DSP is running (not in the

RESET state).

Int Src The Interrupt Source LED is illuminated as long as the V165 has an

interrupt source pending. The interrupt source indicates that a

condition exists for generating an interrupt.

Status The eight status LEDs are driven from the output of a register accessible

by the DSP. These LEDs are used to display error conditions found during the power-on self-test diagnostics. The user also has access to

these LEDs under programmed I/O from the DSP.

#### **Switches**

The V165 has only one front-panel switch which is used to reset the DSP and its associated circuitry. The switch is recessed into the module to prevent accidental activation. A strap option located on the module may be configured to enable or disable the operation of this switch. Please refer to the Strap Options section of this manual for further information.

#### Connectors

The V165 has two fifty-pin male connectors on the front panel of the module. The connector towards the bottom of the module, labeled TTL Inputs, routes 32 digital input lines to a register that the DSP may access. These digital inputs have input protection circuitry to prevent any damage to the module in the case an input is shorted to a high voltage source. The second connector on the V165, labeled Serial Ports, contains the serial port signals from the DSP. This connector also contains two general purpose I/O bits of the DSP. Along with these signals are also two timer/counter bits to/from the DSP.

#### STRAP OPTIONS AND SWITCHES

Before the V165 is installed in the VXI chassis, several user selectable options must be configured. The following indicates the various options and their default configurations as set by the factory.

| PARAMETER                | DEFAULT CONFIGURATION |  |  |  |  |  |

|--------------------------|-----------------------|--|--|--|--|--|

| Logical Address          | 255                   |  |  |  |  |  |

| Bus Request Level        | 3                     |  |  |  |  |  |

| DSP Reset Vector Address | 810000 Hex            |  |  |  |  |  |

| Front Panel Reset        | Enabled               |  |  |  |  |  |

There are other straps located on the module, but they MUST remain in the positions as configured at the factory. The only user configurable straps/switches are those listed above.

## **Logical Address Switches**

The V165 represents one of the 255 devices permitted in a VXIbus system. (Logical Address 0 is reserved for the Slot 0 controller device.) The module is shipped from the factory with its address set for Logical Address 255. This address can be shared by multiple devices in a system that supports dynamic configuration. If the V165 is to be used in a system that does not support dynamic configuration, or in a system where static configuration of the module is desired, the Logical Address must be manually established. This is accomplished by manipulating eight rocker switches located under the access hole in the module's right-side ground shield.

The eight switches represent a binary combination of numbers that range from zero to 255. Use a scribe or other appropriate instrument to set the Logical Address to the desired value.

The bit pattern for the A16 base address is shown below:

| 15 | 14 | 13    |      | 11   | . •  | 09  |     |     | 06  |   |   |   | 02 |   | 00 |  |

|----|----|-------|------|------|------|-----|-----|-----|-----|---|---|---|----|---|----|--|

| 1  | 1  | LA128 | LA64 | LA32 | LA16 | LA8 | LA4 | LA2 | LA1 | 0 | 0 | 0 | 0  | 0 | 0  |  |

Bits 15 and 14 are set to one (VXI defined).

Bits 13 through 6 are user selectable via the address switches LA128-LA1.

Bits 5 through zero are set to "0" to indicate a the start of a block of 64 bytes.

The location of these switches is shown in the diagram in Appendix A.

Setting a switch to the on (closed) position causes the corresponding bit to be a logical 0. Setting a switch to the off (open) position causes the corresponding bit to be a logical 1.

Assume that the user wishes to allow the V165 to be dynamically configured. To allow dynamic configuration, the V165 must be set to logical address 255 (0FF Hex). The following shows the bit pattern for this logical address.

| 15 | 14 |   |   |   | 10 |   |   | 07 |   |   |   |   | 02 | ٠. | 00 |  |

|----|----|---|---|---|----|---|---|----|---|---|---|---|----|----|----|--|

| 1  | 1  | 1 | 1 | 1 | 1  | 1 | 1 | 1  | 1 | 0 | 0 | 0 | 0  | 0  | 0  |  |

To set the V165 for logical address 255 (0FF Hex) place the switches LA128 through LA1 in the off (open) position.

As a second example, assume it is desired to statically configure the V165 for a logical address of 103 (67 Hex). The following diagram shows the bit pattern for this logical address.

| 15 | 14 | 13 | 12 | 11 | 10 | • • • |   |   | 06 |   |   |   | 02 |   | 00 |

|----|----|----|----|----|----|-------|---|---|----|---|---|---|----|---|----|

| 1  | 1  | 0  | 1  | 1  | 0  | 0     | 1 | 1 | 1  | 0 | 0 | 0 | 0  | 0 | 0  |

To set the V165 for logical address 103 (67 Hex), place switches LA128, LA16, LA8 in the (closed) position; and place switches LA64, LA32, LA4, LA2 and LA1 in the off (open) position.

## **Bus Request Level Straps**

The V165 can execute Direct Memory Accesses (DMA) under control of the DSP. Since the V165 implements DMA, the user must select at which level the V165 makes its bus request. The V165 is configured at the factory for Bus Request Level 3.

The diagram in Appendix A shows the location of the Bus Request Level straps. The following chart shows the request levels obtained by the various combination of the straps.

| BR1 | BRO | Bus Request Level |

|-----|-----|-------------------|

| 0   | 0   | Level 0           |

| 0   | 1   | Level 1           |

| 1   | 0   | Level 2           |

| 1   | 1   | Level 3           |

Make sure that all the Bus Grant jumpers for the slot in which the V165 is installed are removed.

## **DSP Reset Vector Address Straps**

There are three straps on the V165 which allow the user to select the reset vector that the DSP uses when a reset condition occurs. Four of these vectors are located in the address space of the PROM and the other four are located in the address space of the dynamic memory (DRAM). The diagram in Appendix A shows the location of the DSP Start Reset Vector Start Address straps. The following shows the reset vectors obtained by the various combinations of the straps.

| BA2 | BA1 | BA0 | DSP Reset Vector Address |

|-----|-----|-----|--------------------------|

| 0   | 0   | 0   | 810000 Hex               |

| 0   | 0   | 1   | 810002 Hex               |

| 0   | 1   | 0   | 810004 Hex               |

| 0   | 1   | 1   | 810006 Hex               |

| 1   | 0   | 0   | 100000 Hex               |

| 1   | 0   | 1   | 100002 Hex               |

| 1   | 1   | 0   | 100004 Hex               |

| 1   | 1   | 1   | 100006 Hex               |

Note: If it is desired to allow the Reset Vector Address to be altered by the VXI accessible DSP Control Register, this reset vector should be set to 810000 Hex. Indeterminate errors may occur if these straps are set to any other value and the DSP Control Register is written to through VXI.

## Front-Panel Reset Strap

The front-panel reset switch may be optionally enabled or disabled. The switch is enabled as configured at the factory. Refer to Appendix A for the location of the RESET Enable/Disable strap.

To disable the front-panel reset switch, place the strap in the D/RST position. To enable the front-panel reset switch, place the strap in the E/RST position.

## PROGRAMMING INFORMATION

## VMEbus/VXIbus Addressing

Of the defined VXIbus Configuration Registers, the V165 implements those required for extended register-based devices. The V165 also contains a set of Operational Registers to monitor and control the functional aspects of the device. Both register sets are described in this section.

Access to the Configuration Registers for all VXIbus modules is available through the VMEbus short address space. The register addresses are located in the upper 16 kilobytes of the A16 address range (C000<sub>16</sub> to FFFF<sub>16</sub>). The setting of the Logical Address switch, or the contents of the Logical Address Register (see below) are mapped into Address lines A6 through A13, thereby establishing a base address for the module somewhere in the range of C000<sub>16</sub> to FFFF<sub>16</sub>.

## **VXIbus Configuration Registers**

Configuration Registers are required by the VXIbus specification so that the appropriate levels of system configuration can be accomplished. The Configuration Registers in the V165 are offset from the base address. Note: the V165 only responds to these addresses if the Short Nonpriviledged Access (29<sub>16</sub>) or Short Supervisory Access (2D<sub>16</sub>) Address Modifier Codes are set for the backplane bus cycle. Table 1 shows the applicable Configuration Registers present in the V165, their offset from the base (Logical) address, and their Read/Write capabilities.

Table 1 - Configuration Registers Configuration (A16) Space

| A16 Offset                          | Read/Write Capability | Register Name               |  |  |  |  |  |

|-------------------------------------|-----------------------|-----------------------------|--|--|--|--|--|

| 0016                                | Read/Write            | ID/Logical Address Register |  |  |  |  |  |

| 0216                                | Read Only             | Device Type Register        |  |  |  |  |  |

| 0416                                | Read/Write            | Status/Control Register     |  |  |  |  |  |

| 0616                                | Read/Write            | Offset Register             |  |  |  |  |  |

| 0816                                | Read Only             | Attribute Register          |  |  |  |  |  |

| 0A <sub>16</sub>                    | Read Only             | Serial Number High Register |  |  |  |  |  |

| 0C <sub>16</sub>                    | Read Only             | Serial Number Low Register  |  |  |  |  |  |

| 0E <sub>16</sub>                    | Read Only             | Version Number Register     |  |  |  |  |  |

| 10 <sub>16</sub> - 19 <sub>16</sub> | Read Only             | Reserved                    |  |  |  |  |  |

| 1A <sub>16</sub>                    | Read Only             | Interrupt Status Register   |  |  |  |  |  |

| A16 Offset                          | Read/Write Capability | Register Name              |  |

|-------------------------------------|-----------------------|----------------------------|--|

| 1C <sub>16</sub>                    | Read/Write            | Interrupt Control Register |  |

| 1E <sub>16</sub>                    | Read Only             | Subclass Register          |  |

| 2016                                | Read Only             | Suffix High Register       |  |

| 22 <sub>16</sub>                    | Read Only             | Suffix Low Register        |  |

| 24 <sub>16</sub> - 3F <sub>16</sub> | Read Only             | Reserved                   |  |

## ID/Logical Address Register

The ID/Logical Address register, which is located at offset 0 from the logical address base, serves two functions, depending on the direction of the VME transfer. When executing a read operation to this register, the data returned indicates the Device Class, the Address Space in which the Operational Registers of the V165 reside, and the Manufacturer's Identification. A write operation to this register is only executed during a dynamic configuration sequence. During the configuration sequence, the Resource Manager assigns a logical address to the V165 by writing the logical address into the lower 8-bits of this register. The format and bit assignments for the ID/Logical Address register are as shown below. Since this register has write-only and read-only bits, two bit patterns are shown.

#### On READ transactions:

| 15 |   |   | 12 |   |   | 09 | ••• | 07 |   |   |   | 03 |   |   | 00 |   |

|----|---|---|----|---|---|----|-----|----|---|---|---|----|---|---|----|---|

| 0  | 1 | 0 | 1  | 1 | 1 | 1  | 1   | 0  | 0 | 1 | 0 | 1  | 0 | 0 | 1  | ı |

| Bit(s)  | Mnemonic                     | Meaning                                                |

|---------|------------------------------|--------------------------------------------------------|

| 15, 14  | Device Class                 | This is an Extended Register-Based device.             |

| 13, 12  | Address Space<br>Requirement | This module requires the use of A16/A32 address space. |

| 11 - 00 | Manufacturer's ID            | 3881 (F29 <sub>16</sub> ) for KineticSystems.          |

#### On WRITE transactions:

|     | 14  |     |     |     |     |     |     | 07    |      |      |      |     |     |     |     |   |

|-----|-----|-----|-----|-----|-----|-----|-----|-------|------|------|------|-----|-----|-----|-----|---|

| N/U | LA128 | LA64 | LA32 | LA16 | LA8 | LA4 | LA2 | LA1 | 1 |

For WRITE transactions, bits fifteen through eight are not used. A write to these bits has no effect on the V165. In Dynamically configured systems (i.e., the Logical Address switches were set to a value of 255), bits seven through zero are written with the new Logical Address value. This write operation is typically executed by a Resource Manager.

## **Device Type Register**

The Device Type Register, which is located at offset 2 from the logical base address, is a readonly register which reflects the Model Code of the V165 and the memory requirements for the V165 Operational Registers. The memory requirement field is used by the Resource Manager to allocate physical address space to the devices located in the VXI chassis. A write operation to this register has no effect on the contents of this register.

The format and bit assignments for the Device Type register are as follows:

| 15 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1  | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

## On READ transactions:

| Bit(s)  | <u>Mnemonic</u> | <u>Meaning</u>                                                                                        |

|---------|-----------------|-------------------------------------------------------------------------------------------------------|

| 15 - 12 | Required Memory | The V165 requires 2 Megabytes of additional memory space. This value varies based on the DRAM option. |

| 11 - 0  | Model code      | Identifies this device as Model V165 (165 <sub>16</sub> ).                                            |

## Status/Control Register

The Status/Control Register, which is located at offset 4 from the logical base address, contains read-only, write-only, and write/read bits. The following describes the bits defined for write and read operations.

The following shows the register layout and the bit pattern for read accesses to the Status/Control register.

| 15      | 14    | 13 | 12 | 11 | 10 | 09 | 80 | 07 | 06 | 05 | 04 | 03  | 02   | 01 | 00  |  |

|---------|-------|----|----|----|----|----|----|----|----|----|----|-----|------|----|-----|--|

| A32 ACT | MODID | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | RDY | PASS | 0  | RST |  |

| $\underline{\mathrm{Bit}(\mathrm{s})}$ | <u>Mnemonic</u> | Meaning                                                                                                                                                                     |

|----------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15                                     | A32 Active      | This bit is read as a one when the V165 is enabled for accesses in A32 address space. This bit is reset to zero on power-up or the assertion of SYSRESET*                   |

| 14                                     | MODID*          | This bit is set to a one if the module is <u>not</u> selected with the MODID line on P2. A zero indicates that the device is selected by a high state on the P2 MODID line. |

| 13 - 04 | Not used | These bits are not used and read as ones.                                            |

|---------|----------|--------------------------------------------------------------------------------------|

| 03      | Ready    | $\boldsymbol{A}$ one indicates the successful completion of register initialization. |

| 02      | Passed   | A one indicates that the $V165$ has failed or is executing its self-test.            |

| 01      | Not used | This bit is not used and read as zero.                                               |

| 00      | RST      | When this bit is reset as a one, the V165 is in a RESET state.                       |

The following shows the register layout and the bit pattern for write accesses to the Status/Control register.

| 15      | 14  | 13  | 12  | 11  | 10  | 09  | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01    | 00  |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|-----|

| A32 ACT | N/U | SFINH | RST |

| Bit(s)  | Mnemonic     | Meaning                                                                                                                                                   |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | A32 Active   | This bit must be set to a one to enable the V165 to be accessed in A32 address space. This bit is reset to zero on power-up or the assertion of SYSRESET* |

| 14 - 02 | Not used     | These bits are not used for write operations.                                                                                                             |

| 01      | Sysfail Inb. | Setting this bit to a one inhibits the V165 from driving the VME SYSFAIL* signal.                                                                         |

| 00      | Reset        | Writing this bit as a one resets the V165. After the bit is set back to a zero, the V165 executes its self-test procedure.                                |

#### Offset Register

The Offset register, which is located at offset 6 from the logical base address, is used for specifying the base address of the V165 operational registers in A32 space. Since the V165 occupies 2 Megabytes of address space, only the most significant 11 bits of this register are used. This register is a 16-bit write/read register with the following bit assignments:

| 15  | 14  | 13  |     |     |     | 09  |     |     | 06  |     | 0.7 |   | 02 |   | 00 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|----|---|----|

| A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A23 | A22 | A21 | 0   | 0 | 0  | 0 | 0  |

| Bit(s)  | Mnemonic  | Meaning                                                                                         |

|---------|-----------|-------------------------------------------------------------------------------------------------|

| 15 - 05 | A31 - A21 | These write/read bits are used for defining the base address of the V165 Operational Registers. |

| 04 - 00 | Not used  | These bits are not used but should be written as zeros.                                         |

After SYSRESET\*, and prior to self-test, all bits are set to zero. Writing to this register is executed by the Resource Manager during the configuration process. The user may then examine this register to determine the base address of the V165 operational registers. After this register is written with the desired base address, the A32 ENABLE bit in the Status/Control register must be set to a one before the V165 Operational Registers may be accessed.

## **Attribute Register**

The Attribute register, which is located at offset 8 from the logical base address, is a 16-bit read-only register which defines the interrupting capabilities of the V165. The V165 is an interrupter with interrupt status functionality, but does not implement an interrupt handler.

The format and bit assignments for the Attribute register are as follows:

| 15 | 14 | 13 |   | 11 |   |   |   |   |   |   |   |   | 02  |     |     |  |

|----|----|----|---|----|---|---|---|---|---|---|---|---|-----|-----|-----|--|

| 1  | 1  | 1  | 1 | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | IR* | IH* | IS* |  |

| Bit(s)  | Mnemonic | Meaning                                                                             |

|---------|----------|-------------------------------------------------------------------------------------|

| 15 - 03 | Not used | A write to these bits has no effect. A read of these bits will return all ones.     |

| 02      | IR*      | The V165 has interrupter control capabilities and returns this bit as a zero.       |

| 01      | IH*      | The V165 does not have interrupt handling capability and returns this bit as a one. |

| 00      | IS*      | The V165 has interrupt status capability and returns this bit as a zero.            |

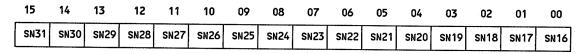

## Serial Number High Register

The Serial Number High register, which is located at offset 0A Hex from the logical base address, is used in combination with the Serial Number Low register to define the serial number of the V165 module. These registers are read-only and a write operation to these registers has no effect.

The format and bit assignments for the Serial Number High register are as follows:

Bit(s) Mnemonic Meaning

15 - 00 SN31 - SN16

These are the upper 16-bits of the 32-bit module serial number. These bits are used in conjunction with bits SN15-SN00 located in the Serial Number Low register.

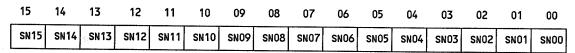

## Serial Number Low Register

The Serial Number Low register, which is located at offset 0C Hex from the logical base address, is used in combination with the Serial Number High register to define the serial number of the V165 module. These registers are read-only and a write operation to these registers has no effect.

The format and bit assignments for the Serial Number Low register are as follows:

Bit(s) Mnemonic Meaning

15 - 00 SN15 - SN00

These are the lower 16-bits of the 32-bit module serial number. These bits are used in conjunction with bits SN31-SN16 located in the Serial Number High register.

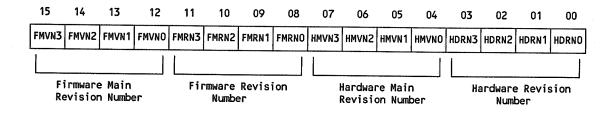

## Version Number Register

The Version Number register, which is located at offset 0E Hex from the logical base address, reflects the current revision level of the hardware and firmware residing on the V165. This is a read-only register and any write operations to this register are ignored.

The format and bit assignments for the Version Number register are as follows:

| Bit(s)  | Mnemonic    | Meaning                                                      |

|---------|-------------|--------------------------------------------------------------|

| 15 - 12 | FMVN3-FMVN0 | These bits reflect the modules firmware main revision level. |

| 11 - 08 | FMRN3-FMRN0 | These bits reflect the modules firmware revision number.     |

| 07 - 04 | HMVN3-HMVN0 | These bits reflect the modules hardware main revision level. |

| 03 - 00 | HDRN3-HDRN0 | These bits reflect the modules hardware revision number.     |

#### **Interrupt Status Register**

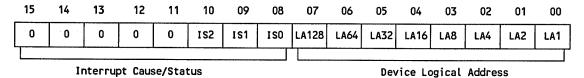

The Interrupt Status register is a 16-bit read-only register which is used for determining the cause of an interrupt generated by the V165. The DSP is the only mechanism on the V165 that may generate an interrupt to VME. The DSP writes to the Source VXI Interrupt register which asserts an interrupt. A 3-bit data pattern that is written to the Source VXI Interrupt register by the DSP is then stored as the cause for the VME interrupt. When the Interrupt Status register is read by a programmed I/O, or by an interrupt acknowledge cycle, the 3-bit pattern is enabled onto data lines 10 through 08. Bits 7 through 0 reflect the logical address of the V165.

The format and bit assignments for the Interrupt Status register are as follows:

| Bit(s)  | Mnemonic        | Meaning                                                                                                              |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------|

| 15 - 08 | Cause/Status    | This field reflects the data pattern written by the DSP to the Source VXI Interrupt register to cause the interrupt. |

| 07 - 00 | Logical Address | Logical address of the V165.                                                                                         |

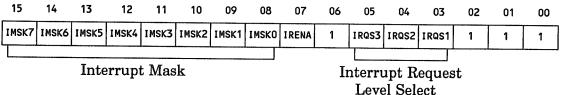

## **Interrupt Control Register**

The Interrupt Control register, which is located at offset 1C Hex from the logical base address, is a 16-bit write/read register which is used to configure the V165 for interrupt generation. The Interrupt Request Level, Interrupt Mask field, and Interrupt Enable bit are located in this register.

The format and bit assignments for the Interrupt Control register are as follows:

|         | -               | Level Select                                                                                                                                                                                                                                                                                                                           |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit(s)  | <u>Mnemonic</u> | Meaning                                                                                                                                                                                                                                                                                                                                |

| 15 - 10 | IMSK7-IMSK0*    | These 8 Interrupt Mask bits are used to enable/disable the generation of an interrupt from the 8 possible sources. These bits enable the various data patterns available for interrupt generation by the DSP writing to the Source VXI Interrupt register. A zero in each location enables the interrupt source and a one disables it. |

| 07      | IR ENA*         | This Interrupt Request Enable bit is used to disable and enable the generation of an interrupt by the V165. Setting this bit to a one disables interrupt generation and clearing this bit to a zero enables interrupts.                                                                                                                |

| 06      | Not Used        | This bit is not used and should be written to a one.                                                                                                                                                                                                                                                                                   |

| 05 - 03 | IRQS3-IRQS1     | The Interrupt Request Select bits are used to select<br>the desired Interrupt Request Level that the V165<br>asserts when an interrupt is sourced. The<br>following shows the binary combination that yield<br>the Interrupt Request Level selections:                                                                                 |

|         |                 | IRQS3 - IRQS2 - IRQS1                                                                                                                                                                                                                                                                                                                  |

|         |                 | 111- disconnected                                                                                                                                                                                                                                                                                                                      |

|         |                 | 110 - Interrupt Request Level 1                                                                                                                                                                                                                                                                                                        |

|         |                 | 101 - Interrupt Request Level 2                                                                                                                                                                                                                                                                                                        |

|         |                 | 100 - Interrupt Request Level 3                                                                                                                                                                                                                                                                                                        |

|         |                 | 011 - Interrupt Request Level 4                                                                                                                                                                                                                                                                                                        |

|         |                 | 010 - Interrupt Request Level 5                                                                                                                                                                                                                                                                                                        |

|         |                 | 001 - Interrupt Request Level 6                                                                                                                                                                                                                                                                                                        |

|         |                 | 000 - Interrupt Request Level 7                                                                                                                                                                                                                                                                                                        |

02 - 00 Not Used

These bits are not used and should be written as ones.

#### **Subclass Register**

The Subclass register, which is located at offset 1E Hex from the logical base address, is a 16-bit read-only register that reflects the subclass of the V165. The V165 is an Extended Register Based Device as the following bit pattern indicates:

| 15 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

| 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |  |

## Bit(s) Meaning

This bit is set to one indicating that this is an VXIbus Extended Device.

14 - 0 These bits are set to 7FFE Hex which indicates that the V165 is an Extended Register Based Device.

## Suffix High Register

The Suffix High register, which is located at offset 20 Hex from the logical base address, is a 16-bit read-only register used in combination with the Suffix Low register to determine the module suffix. The Suffix High register contains the first two ASCII characters of the module suffix and the Suffix Low register contains the second two characters. The suffix shown is for a V165-ZAD1 module.

The format and bit assignments for the Suffix High Register are as follows:

| 15 |   |   |   |   |    |   |   |   |   |   |   |   |   |   |   |

|----|---|---|---|---|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 1 | 0 | 1 | 1 | -0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

This read only register contains the first two characters of the module's suffix ("ZA" = 5A41 Hex)

## Suffix Low Register

The Suffix Low register, which is located at offset 22 Hex from the logical base address, is a 16-bit read-only register used in combination with the Suffix High register to determine the module suffix. The Suffix Low register contains the second two ASCII characters of the module suffix and the Suffix High register contains the first two characters. The suffix shown is for a V165-ZAD1 module.

The format and bit assignments for the Suffix Low Register are as follows:

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 00 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| L | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1  |

This read only register contains the second two characters of the modules suffix ("D1" = 4431 Hex)

## VXI Operational Registers

The Operational registers are the addresses through which the various functions of the V165 are controlled. Since the V165 requires 2 Megabytes of VME address space for the Operational registers, they are positioned in VMEbus Extended Address (A32) space. The base address for these registers is defined by the contents of the Offset register within the Configuration Register set. This offset is typically loaded by the Resource Manager during configuration. The physical address of the Operational registers is calculated by shifting the data found in the Offset register 16-bit locations to the left. For example, if the value 2000 Hex is loaded in the Offset register, the physical address for the base of the Operational registers is at 200000000 Hex.

All registers in A32 address space can be accessed as 32-bit longwords and 16-bit shortwords. These registers cannot be accessed as bytes.

Prior to gaining access to the Operational Registers, the A32 Enable bit (bit 15) must be set in the Status/Control Register. Note: The V165 will only respond to these addresses if the Extended Address Modifier Codes (0F - 0D Hex or 0B - 09 Hex) are set for the bus cycles.

The following chart shows the registers accessible through VXI A32 address space and their offsets from the operational base address.

|   | A32 Address Offset | Access     | Function                     |

|---|--------------------|------------|------------------------------|

|   | 00000000           | Read/Write | Semaphore Flag #1            |

|   | 0000004            | Read/Write | Semaphore Flag #2            |

|   | 00000008           | Read/Write | Semaphore Flag #3            |

|   | 000000C            | Read/Write | Semaphore Flag #4            |

|   | 00000010           | Write-only | DSP Control Register         |

| * | 00000014           | Write-only | Frame Interval Counter       |

|   | 0000018            | Write-only | Generate DSP Interrupt       |

|   | 000001C            |            |                              |

|   | •                  | Reserved   |                              |

|   | 000003C            |            |                              |

| * | 0000040            | Read/Write | Frame Data Selection Word #1 |

| * | 00000044           | Read/Write | Frame Data Selection Word #2 |

| * | 00000048           | Read/Write | Frame Data Selection Word #3 |

|   | •                  |            |                              |

|   | •                  |            |                              |

|    | A32 Address Offset                                                                               | Access     | Function                             |  |  |  |  |  |

|----|--------------------------------------------------------------------------------------------------|------------|--------------------------------------|--|--|--|--|--|

| *  | 000007C                                                                                          | Read/Write | Frame Data Selection Memory Word #16 |  |  |  |  |  |

|    | •                                                                                                |            |                                      |  |  |  |  |  |

|    | 00FFFFF                                                                                          |            |                                      |  |  |  |  |  |

|    | 0100000                                                                                          |            |                                      |  |  |  |  |  |

|    | •                                                                                                | Read/Write | 1 Megabytes Dynamic Memory (DRAM)    |  |  |  |  |  |

|    | •                                                                                                |            |                                      |  |  |  |  |  |

|    | 01FFFFF                                                                                          |            |                                      |  |  |  |  |  |

| NO | NOTE: * Indicates registers that are only available on a V165 with the V165-0001 DIGIBUS option. |            |                                      |  |  |  |  |  |

#### **Semaphore Flags**

The V165 provides four individual Semaphore flags to establish a communication scheme between the DSP and the host computer, via the VME bus. There are four addresses within the VME address space and also four addresses within the DSP address space. To obtain a flag, the requesting processor executes a read to the Semaphore flag desired. If a value of zero is obtained by the processor, the flag is considered transferred to that processor. If a value of 80008000 Hex is received, the flag has already been obtained by the other processor. When the processor that has "won" a flag desires to relinquish it, it simply executes a write operation to the Semaphore Flag address which it wishes to release. Any data may be used to free a flag. Flags are obtained on a first-come first-serve basis. All requests for the flags go through a arbitration sequence to prevent a simultaneous granting of a flag.

The following shows the bit pattern for the 32-bit Semaphore Flags. When accessing these flags as 16-bit quantities, address each flag by its defined offset.

| 31  |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |

|-----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|

| FLG | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | . 0 | 0  | 0  | 0  | 0  | 0  | 0  |

| 15  | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06  | 05 | 04 | 03 | 02 | 01 | 00 |

| FLG | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0  | 0  | 0  |

Bits 31 and 15 are the actual flag bits. Reading these bits as zero indicates that the flag has been transferred. If these bits are read as ones, the flags are currently unavailable. Bits 30 through 16 and 14 through 0 are not used and read as zeros.

As an example of Semaphore Flag use, assume an application program running on the DSP uses a section of the dual-access DRAM for data storage in an array and the host processor also needs access to the same addresses within the DRAM. This dual-access DRAM can be accessed by either the DSP or by VME operations. An arbitration mechanism prevents simultaneous access to the DRAM.

In the example, the host processor cannot alter the contents of the data array while the DSP is in the process of updating the array. Similarly, the DSP cannot alter the contents of the data array while the host processor is in the process of updating the array. Therefore, a communication protocol is required for determining "ownership" of the array.

If either the host processor or DSP need to access the array, it must verify that the array is not "owned" by the other processor. When the DSP desires to update the array, it must execute a read command to the appropriate Semaphore Flag to establish "ownership". If the read command resulted in read data of 80008000 Hex, it must continue to execute the read command until data of zero is received. When data of zero is received, it may then access the array and make any necessary changes to the data within the array. Once the DSP has completed the update, it then releases the flag by executing a write operation to the Semaphore Flag that it obtained earlier. This frees the flag and the arbitration process continues.

#### **DSP** Control Register

D:+(~)

Manamania

The DSP Control register is a write-only register that is used to start/stop DSP operation and to configure the starting address for DSP code execution after a RESET operation.

The RESET bit in this register is used to assert and clear the RESET line to the DSP. Setting this bit to a zero stops the DSP from executing code and places the DSP into a reset state. To enable the DSP for code execution and exit the reset state, set this bit to a one.

After the RESET has been removed from the DSP, the DSP reads the data at address location zero in physical address space to determine where the next instruction resides. The V165 allows for 8 starting address selections. Four of these reside in the PROM and the other four reside in the slow-access DRAM. For further information regarding DSP activity after a RESET condition, please refer to the section entitled DSP Reset.

The following shows the bit pattern for the DSP Control register along with a description of the bits.

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| N/U   |

|     | 14  |     |     |     |     |     |     |     |     |     |     | 03  |     |     | 00    |

| N/U | BA2 | BA1 | BA0 | RESET |

| DIL(S) | <u>Minemonic</u> | Meaning                                                                                                                           |

|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31-04  | Not used         | These bits are not used.                                                                                                          |

| 03-01  | BA2-BA0          | The binary combination of these bits determine the starting address of DSP code execution following a RESET condition as follows: |

| BA2 | BA1   | BA0 | Starting Address |

|-----|-------|-----|------------------|

| 0   | 0     | 0   | 810000           |

| 0   | 0 0 1 |     | 810002           |

| 0   | 1     | 0   | 810004           |

| 0   | 1     | 1   | 810006           |

| 1   | 0     | 0   | 100000           |

| 1   | 0     | 1   | 100002           |

| 1   | 1 1   |     | 100004           |

| 1   | 1     | 1   | 100006           |

00 Reset

This bit is used to assert/clear the RESET line of the DSP. Setting this bit to a one enables the DSP to execute code. Setting this bit to a zero places the DSP in the RESET state.

## Frame Interval Register

The Frame Interval register is only available when the V165 is equipped with the V165-0001 DIGIBUS option. This 32-bit write/read register is used to specify the interval at which the V165 stores DIGIBUS data frames. The Capture bit located in this register enables/disables the capturing of DIGIBUS data by the V165-Bxx1.

The FC7 through FC0 bits define the interval at which frames are captured from the DIGIBUS. Setting this field to zero instructs the DIGIBUS capture circuitry to store every frame of data that it sees on the DIGIBUS. To capture every other frame of data, set this field to one. The maximum value for this field is 255. This frame interval selection can ease the burden on the DSP when receiving data from the DIGIBUS when not every frame of data is required for the application.

The CAPTURE bit in the Frame Interval register is used to enable and disable the capturing of data from the DIGIBUS. Setting this bit to a one enables the capturing of data from the DIGIBUS. After the bit is set, the capture mechanism waits for the start of a frame before storing data. The storage of data will not start in the middle of a frame.

The following shows the bit pattern for the Frame Interval register.

|   |    |    |    | 28 |    |    |    |     |     |     |     |     |     |     |     |     |

|---|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|   | 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08  | 07  | 06  | 05  | 04  | 03  | 02  | 01  | 00  |

| L | 0  | 0  | 0  | 0  | 0  | 0  | 0  | CAP | FC7 | FC6 | FC5 | FC4 | FC3 | FC2 | FC1 | FC0 |

| Bit(s) | <u>Mnemonic</u> | Meaning                                                                                                                           |

|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31-09  | Not used        | These bits are not used and read as zeros.                                                                                        |

| 08     | CAP             | This bit is used to enable/disable DIGIBUS data capturing. Setting this bit to a one enables capture and a zero disables capture. |

| 07-00  | FC7-FC0         | Frame interval bits 7 through 0 control the interval at which DIGIBUS frames are store.                                           |

#### Frame Data Selection Words

The Frame Data Selection Words are only used with the V165-Bxx1 DIGIBUS option for the V165. These 16 16-bit words control which samples within each frame are stored. The selection words have a bit location for each of the 256 samples within a frame. The maximum number of samples in any given frame is 256.

Setting a bit to a one enables the corresponding data sample to be stored from the DIGIBUS. A zero in any given location indicates that the sample is to be discarded. The following chart shows the bit layout for the selection words. Bits 31 through 16 of these longwords are not used.

| a. 169 s, | 15         | 14         | 13         | 12         | 11         | 10         | 09         | 08         | 07         | 06         | 05         | 04         | 03         | 02         | 01         | 00         |     |

|-----------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-----|

|           | SMP<br>15  | SMP<br>14  | SMP<br>13  | SMP<br>12  | SMP<br>11  | SMP<br>10  | SMP<br>9   | SMP<br>8   | SMP<br>7   | SMP<br>6   | SMP<br>5   | SMP<br>4   | SMP<br>3   | SMP<br>2   | SMP<br>1   | SMP<br>0   | :40 |

|           | SMP<br>31  | SMP<br>30  | SMP<br>29  | SMP<br>28  | SMP<br>27  | SMP<br>26  | SMP<br>25  | SMP<br>24  | SMP<br>23  | SMP<br>22  | SMP<br>21  | SMP<br>20  | SMP<br>19  | SMP<br>18  | SMP<br>17  | SMP<br>16  | :44 |

|           |            |            |            |            |            |            |            |            | 6          | •          |            |            |            |            |            |            | •   |

|           |            |            |            |            |            |            |            |            | •          |            |            |            |            |            |            |            |     |

|           | SMP<br>255 | SMP<br>254 | SMP<br>253 | SMP<br>252 | SMP<br>251 | SMP<br>250 | SMP<br>249 | SMP<br>248 | SMP<br>247 | SMP<br>246 | SMP<br>245 | SMP<br>244 | SMP<br>243 | SMP<br>242 | SMP<br>241 | SMP<br>240 | :7C |

#### DRAM

The V165 has 1 Megabyte of Dynamic Random Access Memory (DRAM). This memory is accessible by both the DSP and the host processor. The starting address of this memory is at an offset of 100000 Hex from the operational registers base address and continues to 1FFFFF Hex. This memory is configured as 32-bit longwords, but may be accessed as 16-bit shortwords.

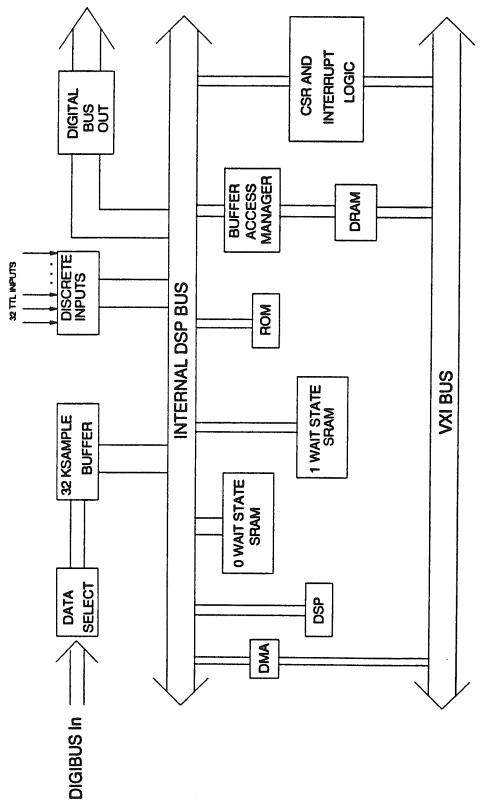

#### **DSP Architecture**

The basic architecture of the DSP and its support circuitry are shown in the following block diagram.

Model V165-xAx1 Rev. 10-26-00

The DSP is a Texas Instruments (TI) TMS320C30 40 Megahertz component with a 50 nanosecond (ns) cycle time. This means that the DSP may accesses data/code from any zero wait-state external component in 50 nanoseconds. External devices that require one wait-state access cause the DSP to add one additional cycle, increasing the access time to 100 nanoseconds.

The DSP has two busses, a primary bus and an expansion bus. The primary bus contains 32-bits of data and 24-bits of addressing. The expansion bus contains 32-bits of data and 13-bits of addressing. In the V165 implementation, all the memory components (DRAM, PROM,..) are located on the primary bus. The expansion bus is used for other peripheral communications such as semaphore flags, Direct Memory Access (DMA) interface to VME, and VXI Trigger Line access.

#### ALL DSP ADDRESSING IS 32 BITS WIDE.

The primary bus is used to communicate with the following:

128 Kilobyte zero wait-state Static RAM

128 Kilobyte one wait-state Static RAM

128 Kilobyte one wait-state PROM

1 Megabyte dual access Dynamic RAM

DRAM Buffer Access Manager

32 Ksample DIGIBUS Static RAM (V165-Bxx1 option only)

The expansion bus is used to communicate with the following peripherals:

Digital Input Register

DMA Control Registers

VXI Interrupt Registers

VXI Trigger Line Access Registers

Front Panel LED Display Register

SYSFAIL Register

DIGIBUS Control Registers (V165-Bxx1 option only)

## DSP Memory Map

The following diagram shows the memory layout for the DSP.

|       | 0 Wait State SRAM<br>128 Kbytes | 0000001<br>007FFF  |

|-------|---------------------------------|--------------------|

|       | 1 Wait State SRAM<br>128 Kbytes | 008000H<br>00FFFH  |

|       |                                 | 10000h             |

|       | Reserved                        | OFFFFFh            |

|       |                                 | -                  |

|       | Slow Access DRAM                | 100000h            |

|       | 1 Mbyte                         | 13FFFFh            |

|       | 64Kbyte DIGIBUS Memory          | 500000h            |

|       |                                 | 507FFFh            |

|       | Reserved                        | 508000h<br>5FFFFFh |

|       | DRAM Prefetch Address           | 600000h<br>600003h |

| 47.00 | Reserved                        | 600004h            |

|       |                                 | 7FFFFFh            |

|       | Semaphore Flags                 | 800000h<br>800003h |

|       | Reserved                        | 800004h            |

| ļ     |                                 | 803FFFh            |

|       | Expansion Bus Peripherals       | 804000h<br>804010h |

|       | Reserved                        | 804011h<br>807FFFh |

| l     | DSP Internal Memory             | 808000h            |

|       | Mapped Registers                | 8097FFh            |

|       | DSP Internal RAM Block<br>O     | 809800h<br>809BFFh |

|       | DSP Internal RAM Block<br>1     | 809C00h<br>809FFFh |

| -     | Reserved                        | 80A000h<br>80FFFFh |

|       | 128 Kbyte PROM                  | 810000h<br>817FFFh |

| -     | Reserved                        | 818000h<br>8FFFFFh |

| -     | Buffer Access Manager           | 900000h            |

|       | DRAM                            |                    |

|       | 1 Mbyte                         | 93FFFFh            |

| _     | Reserved                        | D00000h<br>FFFFFFh |

| -     |                                 |                    |

The following chart indicates the address assignments of the peripheral components connected to the DSP and the bus to which it is connected.

| 00000-0007FFF       | 128 Kbyte zero wait-state SRAM         | Primary    |

|---------------------|----------------------------------------|------------|

| 008000-00FFFF       | 128 Kbyte one wait-state SRAM          | Primary    |

| 010000-0FFFFF       | Reserved                               | Finnary    |

| 100000-13FFFF       | 1 Mbyte Slow Access DRAM               | Primary    |

| 500000-507FFF       | 64 Kbyte DIGIBUS SRAM (V165-Bxx1 only) | ,          |

| 508000-5FFFFF       | Reserved                               | Primary    |