Interconnect Slot-0 Controller

User's Manual

August 27, 2004

(C) 2001, 2003, 2004 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

## CONTENTS

| UNPACKING AND INSTALLATION                      |                                         |

|-------------------------------------------------|-----------------------------------------|

| Logical Address Switches                        |                                         |

| Module Insertion                                | *************************************** |

|                                                 |                                         |

| FRONT PANEL INFORMATION                         |                                         |

| Node Address Switch                             |                                         |

| Option Specific Connectors                      | 4                                       |

| SMB Connector Option                            |                                         |

| Triggor Expansion Connector Option              |                                         |

| 1 1001 Optio                                    |                                         |

| Serial Port                                     | ······ (                                |

|                                                 |                                         |

| VXIBUS CONNECTORS                               |                                         |

| STRAPPING INFORMATION                           |                                         |

| Strap Descriptions                              | 10                                      |

| Strap Descriptions VXIbus Slot0 Configuration   | 11                                      |

| VXIbus Slot0 Configuration                      | 12                                      |

| V160xyz3 Slot0 Configuration  Bus Request Level | 12                                      |

| Bus Request Level Interrupt Handler             | 13                                      |

| Interrupt Handler                               | 13                                      |

| TTL Trigger I/O                                 | 13                                      |

|                                                 |                                         |

| SWITCHING INFORMATION                           |                                         |

| Switch Descriptions                             | 15                                      |

| V 100 Sloto Configuration                       |                                         |

| Dus Request Level                               | 10                                      |

| interrupt transier                              | 4.0                                     |

| 11D 111gg01 I/O                                 |                                         |

| CLK10 Source                                    | 20                                      |

|                                                 |                                         |

| PROGRAMMING INFORMATION                         | 21                                      |

| VMEbus/VXIbus Addressing                        | 21                                      |

| A16 Base Address                                | 21                                      |

| VXIbus Configuration Registers                  |                                         |

| V160-XYZ3 INTERNAL REGISTER DESCRIPTIONS        | 33                                      |

|                                                 |                                         |

| SPECIAL HIGHWAY INSTRICTIONS                    | 46                                      |

| Addressed Slave Trigger Instruction             | 46                                      |

| Stoudoust Trigger Instruction                   | 47                                      |

| LIST PROCESSING INSTRUCTION FORMATS             | 48                                      |

| /XI/VME INSTRUCTIONS                            | 49                                      |

| /XI/VME SINGLE TRANSFER INSTRUCTIONS            |                                         |

|                                                 | 52                                      |

| VXI/VME BLOCK TRANSFER INSTRUCTIONS           | 54    |

|-----------------------------------------------|-------|

| VXI/VME SINGLE INLINE WRITE INSTRUCTION       | 57    |

| SPECIAL INSTRUCTIONS                          | 50    |

| Trait mistraction                             | ćo    |

| Dianch instructions                           |       |

| Onconditional Branch Instruction              |       |

| Source Trigger Generate Interrupt Instruction |       |

| Generate Interrupt Instruction                |       |

| CONTROL/STATUS RGISTER                        | 62    |

| LISTPROCESSING OPERATION                      | 60    |

| Timer Initiated List Execution                | 62    |

| Multibuffer Memory Operation                  |       |

| Demand Messages                               | 65    |

| 1 toolt Disable I uncholl                     |       |

| DSP Firmware                                  | 67    |

| Serial Port Functions                         | 68    |

| APPENDIX                                      | 68    |

|                                               | 70-76 |

## LIST OF FIGURES

| Figure 1     | V160-xyz3 Logical Address Switches                   |

|--------------|------------------------------------------------------|

| Figure 2     | V160-xyz3 Logical Address Switches                   |

| Figure 3     | Front Panel Layout                                   |

| Figure 4     | Node Address 3<br>Stranning 4                        |

| Figure 5     | Strapping                                            |

| Figure 6     | 1 1 2 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1              |

|              | Switch Setting 3                                     |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              | LIST OF TABLES                                       |

|              | LIST OF TABLES                                       |

| Table 1. St  | tatus LED Definitions                                |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

|              |                                                      |

| Table 14C    | CLK 10 Configurations 20                             |

| Table 15. C  | Configuration Registers Configuration (A16) Space 22 |

|              |                                                      |

|              |                                                      |

| Table 18. Ti | imer Initiated List Processing Example               |

|              | 64                                                   |

# **Interconnect VXI Slot-0 Controller**

# Part of the high-throughput, low-latency Grand Interconnect

V160

#### **Features**

- Provides a VXIbus interface for the Interconnect Highway

- Up to 126 controllers per Interconnect network

- Provides full VXI Slot-0 functionality

- Provides full throughput with a 2 km maximum distance between fiber-optic nodes

- Provides up to 10 Mbyte/s highway throughput

- · Includes a high-speed command processor

- Supports buffer memory options

- TTL Trigger Expansion

### **Typical Applications**

- · Jet aircraft engine test cells

- · Rocket engine test cells

- Missile testing

- Wind tunnel data acquisition and control

- Aerospace testing

- Nuclear accelerator control and monitoring

- High-performance ATE

- Multi-mainframe VXIbus systems

- Distributed VXIbus systems

- · Systems requiring galvanic isolation

# General Description (Product specifications and descriptions subject to change without notice.)

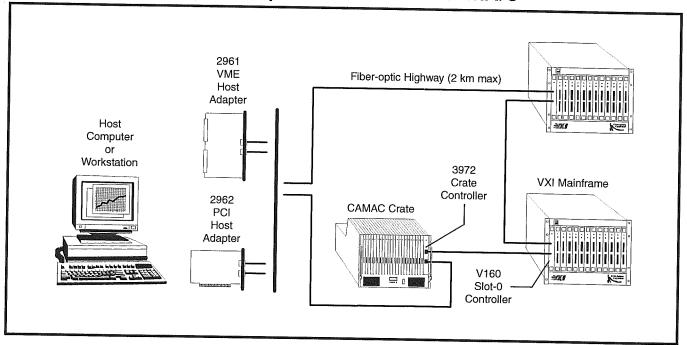

The Grand Interconnect connects multiple I/O chassis to a host computer, providing a high-throughput, deterministic data acquisition and control system. A complete Grand Interconnect system includes an Interconnect Host Adapter (IHA), up to 126 I/O nodes that may include VXI Slot-0 controllers and/or CAMAC (IEEE 583) crate controllers, and a fiber-optic highway. The system supports distances between nodes up to 2 km (6560 ft).

The V160 is a single-width, C-size, VXIbus controller that interfaces the Interconnect Highway to a VXI chassis. It is a slave device on the highway and receives its commands from an Interconnect Host Adapter. This module meets all the requirements of a VXIbus Slot-0 controller, including a MODID register for geographic addressing, a "CLK10" 10 MHz source, TTL/ECL trigger functions, and VXI interrupt handling. Interrupts generated in the VXI chassis are acknowledged by the V160, causing a demand message to be transmitted over the highway to notify the host.

The V160 communicates with the VXIbus using A32, A24, or A16 addressing modes as well as D32, D16, or D08 (EO) data transfers. All access via VXIbus is performed using register-based commands. This module includes a 16 MHz clock driver, a data transfer bus priority arbiter, and an interrupt handler.

List processing is included to allow the V160 to execute a sequence of preloaded write or read commands to selected VXI module registers. The list can be triggered by a software command from the Interconnect Host Adapter (IHA); an internal, crystal-controlled, programmable counter/timer; an externally supplied trigger source; a preselected interrupt; or a TTL/ECL trigger line. During setup the list is downloaded over the highway. Once execution begins, data received from VXIbus read operations is stored in a 2 kbyte FIFO memory for transmission to the host computer. For applications that require more than 2 kbytes of storage for timer-initiated lists, a 4 Mbyte buffer memory option (V160-wB22) is available. For VXIbus write operations, data may be embedded in the list or extracted from a FIFO memory.

The Interconnect Host Adapter also contains a list processor. Its list memory can be used for all I/O transfers. With this approach, both the I/O register addresses and the data must be transmitted over the highway which reduces overall throughput. However, a high-performance list operation for a multi-chassis system can be obtained by using an instruction in the IHA's list processor to transfer a block of read or write data for all operations in a chassis; then the list processor in each V160 can select the sequence of I/O registers to be read or written. This causes only data to be transmitted over the highway, resulting in maximum I/O throughput. The full 10 Mbyte/s data throughput can be achieved by the V160, limited only by the IHA and VXI module transfer capabilities. The I/O list can be driven by a programmable timer with rates ranging from less than 0.06 Hz to 500 kHz.

# Grand Interconnect Configuration Options with CAMAC and/or VXI I/O

| Item                             | Specification |                                                |        |   |

|----------------------------------|---------------|------------------------------------------------|--------|---|

| Connectors                       |               |                                                |        |   |

| Fiber Optic (Hwy In and Hwy Out) | ST-Type Co    | nnectors                                       |        |   |

| Serial Port (Test interface)     | 9P "D"        |                                                |        |   |

| Clock I/O                        | SMB (V160-    | ·Axyz)                                         |        |   |

| Trigger I/O                      | SMB (V160-    |                                                |        |   |

| Trigger Out (A and B)            | SMB (V160-    | Axyz)                                          |        |   |

| Inhibit                          | SMB (V160-    | Axyz)                                          |        |   |

| Execute List                     |               | SMB (V160-Axyz)                                |        |   |

| Trigger Expansion                | 26 Position I | 26 Position High Density Connector (V160-Bxyz) |        |   |

| Backup                           |               | 5.54 mm Power Connector                        |        |   |

| Power Requirements               | +5 V          | -5.2 V                                         | -2 V   |   |

| AA1z                             | 6.7 A         | 250 mA                                         | 250 mA |   |

| AByz                             | 8.5 A         | 250 mA                                         | 250 mA |   |

| BA1z                             | 7.0 A         | 250 mA                                         | 250 mA | , |

| BByz                             | 8.8 A         | 250 mA                                         | 250 mA |   |

| Environmental and Mechanical     |               |                                                |        |   |

| Temperature range                |               |                                                |        |   |

| Operational                      | 0°C to 50°C   | 0°C to 50°C                                    |        |   |

| Storage                          | -25°C to +75  | -25°C to +75°C                                 |        |   |

| Relative humidity                | 0 to 85%, no  | 0 to 85%, non-condensing, to 40°C              |        |   |

| Cooling requirements             | 10 CFM        | I                                              |        |   |

| Dimensions                       | 340 mm x 23   | 340 mm x 233.35 mm x 30.48 mm (C-size VXIbus)  |        |   |

| Front-panel potential            |               | Chassis ground                                 |        |   |

## **Ordering Information**

Model V160-AA13 Interconnect VXI Slot-0 Controller

Model V160-AB13 Interconnect VXI Slot-0 Controller with 1 Mbyte Memory

Model V160-AB23 Interconnect VXI Slot-0 Controller with 4 Mbyte Memory

Model V160-BA13 Interconnect VXI Slot-0 Controller with Trigger Line Interface

Model V160-BB13 Interconnect VXI Slot-0 Controller with 1 Mbyte Memory and Trigger Line Interface

Model V160-BB23 Interconnect VXI Slot-0 Controller with 4 Mbyte Memory and Trigger Line Interface

Model V160-0001 4 Mbyte Memory Factory Upgrade Model V160-0002 1 Mbyte Memory Factory Upgrade

#### **Related Products**

| Model 2961      | VME Interconnect Host Adapter       |

|-----------------|-------------------------------------|

| Model 2962      | PCI Interconnect Host Adapter       |

| Model 3972      | Interconnect CAMAC Crate Controller |

| Model 5802-Lxyz | Cable—50 μm Fiber-optic             |

| Model 5802-Nxyz | Cable—62.5 µm Fiber-optic           |

| Model 5856-Bxyz | Cable—9S "D" to Unterminated        |

| Model 5919-Z1A  | Connector—SMB Cable-type            |

| Model 5930-Z1A  | Connector—9S "D"                    |

## UNPACKING AND INSTALLATION

The Model V160-xyz3 is shipped in an anti-static bag within a Styrofoam packing container. Carefully remove the module from its anti-static bag and prepare to set the various options to conform to the operating environment.

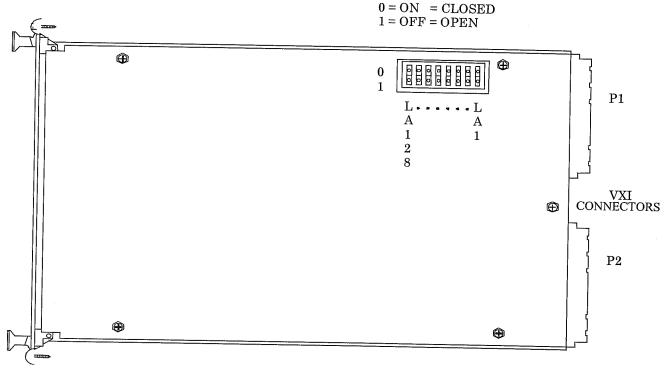

## LOGICAL ADDRESS SWITCHES

The V160-xyz3 is a Slot 0 capable device. It is shipped from the factory configured for Slot 0 operation with its Logical Address Switches statically configured for Logical Address 0. If the V160-xyz3 is to operate as the Slot 0 device, then its Logical Address must be set for Logical Address 0. If it is not, these switches must be set for Logical Address 1 to 255. Logical Address 255 can be shared by multiple devices in a system that supports Dynamic Configuration. If a non-Slot 0 V160-xyz3 is to be used in a system that does not support Dynamic Configuration, or in a system where static configuration of the module is desired, the Logical Address must be manually established. This is accomplished by manipulating the eight rocker switches located under the access hole in the module's right-side ground shield. (Refer to Figure 1.)

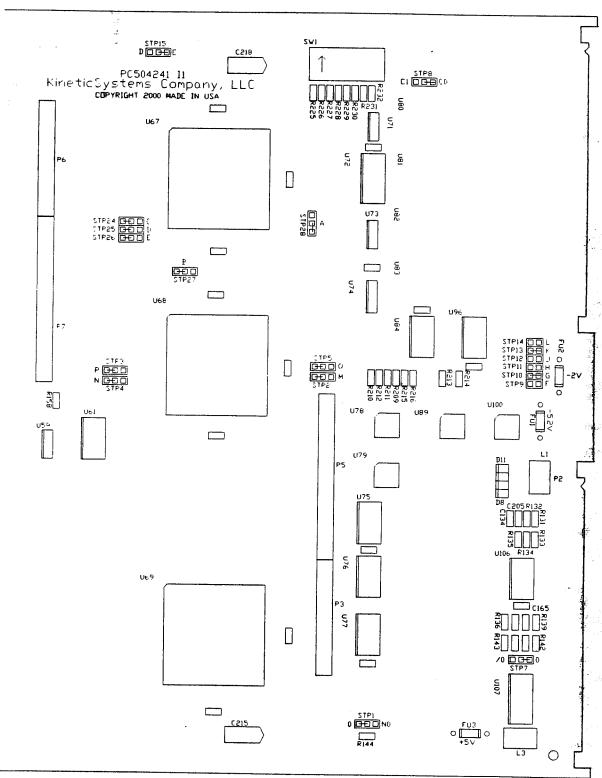

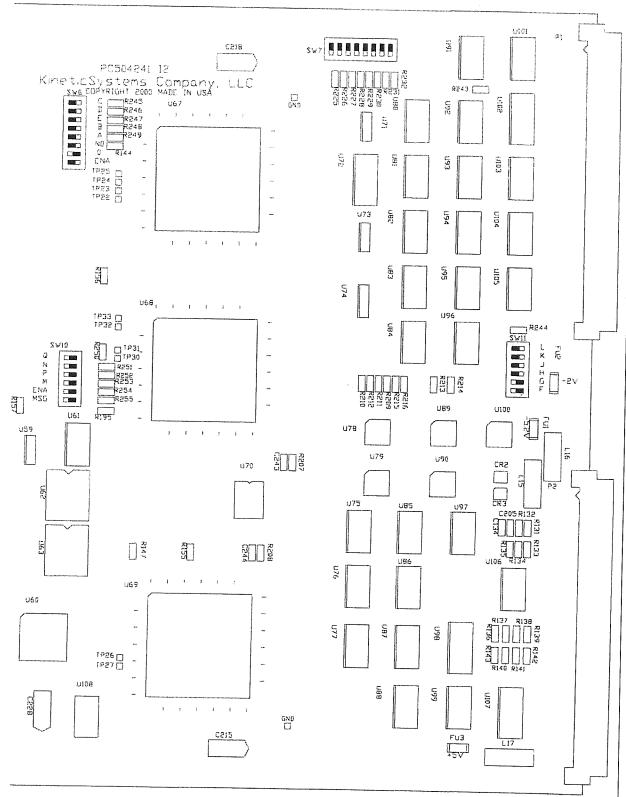

Figure - 1 V160-xyz3 Logical Address Switches

These switches represent a binary combination of numbers that range from zero to 255. Use a scribe or other appropriate instrument to set the Logical Address to the desired value. A switch pushed down on the OPEN side is ON (1). For a Logical Address of zero, all switches should be pushed down on the closed (top as viewed in Figure 1) side.

The Logical Address is used to define the A16 base address of the V160-xyz3's VXIbus defined configuration registers. Further explanation on calculating this base address can be found in the section on VXIbus Configuration Registers.

#### MODULE INSERTION

Depending on the version of the V160 there are either straps loaded or switches loaded for the configuration of the device.

The V160-xyz3 is a C-sized, single width VXIbus module. This module is shipped from the factory configured for Slot 0 operation. Installing a Slot 0 configured V160-xyz3 in any other slot (other than Slot 0) can result in damage to it and other components in the system. Refer to the section on V160-xyz3 Slot 0 Configuration for more information.

CAUTION: TURN OFF MAINFRAME POWER BEFORE INSERTING OR REMOVING MODULE.

WARNING: REMEMBER TO REMOVE THE INTERRUPT ACKNOWLEDGE AND BUS GRANT DAISY CHAIN JUMPERS BEFORE INSERTING MODULE.

The VXIbus backplane must be properly configured before inserting a module and applying power. The Bus Grant and Interrupt Acknowledge daisy chain jumpers should be installed in any unoccupied slot.

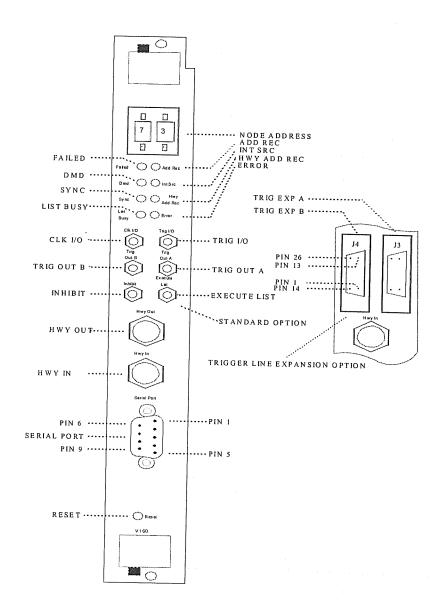

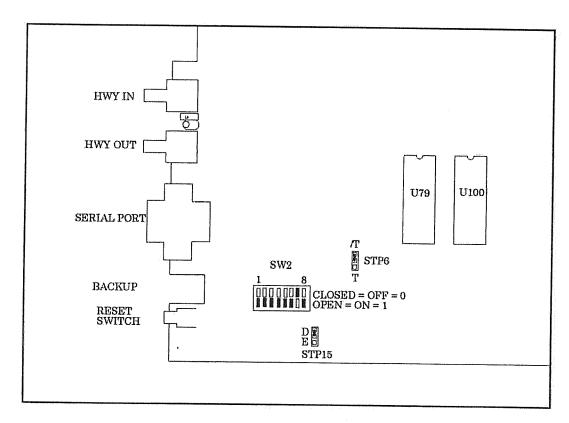

Figure 2 - V160-xyz3 Front Panel Layout

## FRONT PANEL INFORMATION

This section describes the connectors, status LEDs, etc. that appear on the front panel and their functions.

## NODE ADDRESS SWITCH

The Node Address Switch establishes the V160-xyz3's highway node address. This switch contains two digits in hexadecimal format. Each slave on the highway must have a unique node address, ranging from

Figure 3 - V160 Node Address Switch

$1\ (01_{16})$  to  $127\ (7F_{16}).$  Node address  $0\ (00_{16})$  is reserved and should not be used.

Figure 3 shows the node address switch set to a value of  $73_{16}$  (115). Notice the most significant digit is on the left and the least is on the right.

#### LEDS

The V160-xyz3 has eight LEDs located on the front panel to display status information. All LEDs are one-shot extended. Table 1 lists each LED and defines when they are active (lighted).

Table 1. Status LED Definitions

| Description                                                                     |  |

|---------------------------------------------------------------------------------|--|

| Failed - Onboard DSP is executing or has failed its self-test.                  |  |

| Address Recognized - Transfer to V160's Configuration Registers was successful. |  |

| Demand - A demand message has been placed in the Demand FIFO.                   |  |

| Interrupt Source - V160 is generating an interrupt source signal.               |  |

| Synchronization - Indicates valid highway activity or synchronization message.  |  |

| Highway Address Recognized - V160 recognizes that it is the addressed node.     |  |

| List Busy - List Processor is executing instructions from the List Memory.      |  |

| Error (R) Error - A parity error has occurred on the highway.                   |  |

|                                                                                 |  |

## OPTION SPECIFIC CONNECTORS

The V160-xyz3 has a set of front panel connectors used for clocks and triggers, which differ depending on the option. The V160-Ayz3 has six SMB connectors, while the V160-Byz3 has two 26-pin SCSI II type connectors.

## SMB CONNECTOR OPTION

All V160-xyz3 options have front panel mounted SMBs. Table 2 describes the function of each.

Table 2. SMB Connector Descriptions

| Description                                                                            |

|----------------------------------------------------------------------------------------|

| 10 MHz system clock - Can be configured with straps for input or output.               |

| Trigger Input/Output - Configured with straps to route a TTL Trigger Line in/out.      |

| Internal Trigger Output B signal - See Internal Register description.                  |

| Internal Trigger Output A signal - See Internal Register description.                  |

| Reflects the state of Inhibit bit in the Control/Status Register (Internal Registers). |

| Input trigger that may be used to start list execution.                                |

| 3400000                                                                                |

Each of these signals appears on the center pin of the SMB connector. The shell of these connectors is connected to module ground.

## TRIGGER EXPANSION CONNECTOR OPTION

V160-Byz3 options have two 26-position SCSI II type socket connectors that replace the SMB connectors and contains some additional signals. This series of options buffers and routes the VXIbus TTL Trigger to these front panel connectors.

Table 3. V160-xyz3 Trigger Expansion Pinouts

| 1 Tigger Expansion Pinouts |               |  |                          |               |  |

|----------------------------|---------------|--|--------------------------|---------------|--|

| Trigger Expansion B - J4   |               |  | Trigger Expansion A - J3 |               |  |

| Pin Description            | Pin Number(s) |  | Pin Description          | Pin Number(s) |  |

| TTL Trigger 0 I/O          | 1             |  | TTL Trigger 0 I/O        | 1             |  |

| TTL Trigger 1 I/O          | 2             |  | TTL Trigger 1 I/O        | 2             |  |

| TTL Trigger 2 I/O          | 3             |  | TTL Trigger 2 I/O        | 3             |  |

| TTL Trigger 3 I/O          | 4             |  | TTL Trigger 3 I/O        | 4             |  |

| TTL Trigger 4 I/O          | 5             |  | TTL Trigger 4 I/O        | 5             |  |

| TTL Trigger 5 I/O          | 6             |  | TTL Trigger 5 I/O        | 6             |  |

| TTL Trigger 6 I/O          | 7             |  | TTL Trigger 6 I/O        | 7             |  |

| TTL Trigger 7 I/O          | 8             |  | TTL Trigger 7 I/O        | 8             |  |

| CLK10 Input                | 9             |  | CLK10 Output             | 9             |  |

| Trigger Expansion B - J4 |               |  |  |

|--------------------------|---------------|--|--|

| Pin Description          | Pin Number(s) |  |  |

| *No Connection           | 10            |  |  |

| *No Connection           | 11            |  |  |

| Execute List Input       | 12            |  |  |

| *No Connection           | 13            |  |  |

| Ground                   | 14-26         |  |  |

| Trigger Expansion A - J3 |               |  |

|--------------------------|---------------|--|

| Pin Description          | Pin Number(s) |  |

| Trigger A Output         | 10            |  |

| Trigger B Output         | 11            |  |

| Execute List Output      | 12            |  |

| Inhibit Output           | 13            |  |

| Ground                   | 14-26         |  |

<sup>\*</sup> No internal connection is made.

Expansion connector part number - AMP 749611-1.

Mating 26 position male cable connector - Honda PCS-XE26M ( #28 or #30 AWG discrete wire ). Backshell for mating connector - Honda PCS-XE26LA or PCS-XE26LKA.

#### **FIBEROPTIC**

The V160-xyz3's two front panel mounted ST type connectors serve as the input and output for the fiberoptic highway. The connector labeled Hwy In is the highway input. This input should be connected to the highway output connector of the driver or another slave. Conversely, the Hwy Out is the output connector and should be connected to a driver or slave highway input connector. Fiberoptic highway connections should be made using  $62.5/100\mu m$  fiberoptic cables.

## SERIAL PORT

The serial port connector is a 9-position subminiature D type connector with pins. It is used as a general purpose serial interface to the V160-xyz3. For more information on the serial port, see the section on Serial Port Functions. The connector's pinout is shown in Table 4. Any standard 9-position subminiature D type socket connector may be used as a mating connector.

Table 4. Serial Port Connector Pinout

| Pin Number | Pin Description         |        |  |

|------------|-------------------------|--------|--|

| 2          | Receive                 | (RXD*) |  |

| 3          | Transmit                | (TXD*) |  |

| 5          | Ground                  | (GND)  |  |

| 1, 4, 6, 9 | No internal connection. |        |  |

## **VXIBUS CONNECTORS**

The V160-xyz3 is a C-sized VXIbus module and uses both the P1 and P2 connectors. Tables 5 and 6 list the connections made.

Table 5. VXIbus P1 Connections

| Table 5. VXIbus P1 Connections |               |               |               |

|--------------------------------|---------------|---------------|---------------|

| Pin                            | Row A         | Row B         | Row C         |

| 11                             | D00           | BBSY*         | D08           |

| 2                              | D01           | No Connection | D09           |

| 3                              | D02           | No Connection | D10           |

| 4                              | D03           | BG0IN*        | D11           |

| 5                              | D04           | BG0OUT*       | D12           |

| 6                              | D05           | BG1IN*        | D13           |

| 7                              | D06           | BG10UT*       | D14           |

| 8                              | D07           | BG2IN*        | D15           |

| 9                              | GND           | BG2OUT*       | GND           |

| 10                             | SYSCLK        | BG3IN*        | SYSFAIL*      |

| 11                             | GND           | BG3OUT*       | BERR*         |

| 12                             | DS1*          | BR0*          | SYSRESET*     |

| 13                             | DS0*          | BR1*          | LWORD*        |

| 14                             | WRITE*        | BR2*          | AM5           |

| 15                             | GND           | BR3*          | A23           |

| 16                             | DTACK*        | AM0           | A22           |

| 17                             | GND           | AM1           | A21           |

| 18                             | AS*           | AM2           | A20           |

| 19                             | GND           | AM3           | A19           |

| 20                             | IACK*         | GND           | A18           |

| 21                             | IACKIN*       | No Connection | A17           |

| 22                             | IACKOUT*      | No Connection | A16           |

| 23                             | AM4           | GND           | A15           |

| 24                             | A07           | IRQ7*         | A14           |

| 25                             | A06           | IRQ6*         | A13           |

| 26                             | A05           | IRQ5*         | A12           |

| 27                             | A04           | IRQ4*         | A11           |

| 28                             | A03           | IRQ3*         | A10           |

| 29                             | A02           | IRQ2*         | A09           |

| 30                             | A01           | IRQ1*         | A08           |

| 31                             | No Connection | No Connection | No Connection |

| 32                             | +5 V          | +5 V          | +5V           |

|                                |               |               |               |

Table 6. VXIbus P2 Connections

| Pin         Row A         Row B         Row C           1         ECLTRG0         +5 V         CLK10+           2         -2 V         GND         CLK10-           3         ECLTRG1         No Connection         GND           4         GND         A24         -5.2 V           5         MODID12         A25         LBUSC00           6         MODID11         A26         LBUSC01           7         -5.2 V         A27         GND           8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID08         A31         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09                                                          | Table 6. VAlbus P2 Connections          |               |               |               |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------|---------------|---------------|--|

| 1         ECLTRG0         +5 V         CLK10+           2         -2 V         GND         CLK10-           3         ECLTRG1         No Connection         GND           4         GND         A24         -5.2 V           5         MODID12         A25         LBUSC00           6         MODID11         A26         LBUSC01           7         -5.2 V         A27         GND           8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC03           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC06           15         MODID04         D19         LBUSC08           18         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V                                                   | Pin                                     | Row A         | Row B         | Row C         |  |

| 2         -2 V         GND         CLK10-           3         ECLTRG1         No Connection         GND           4         GND         A24         -5.2 V           5         MODID12         A25         LBUSC00           6         MODID11         A26         LBUSC01           7         -5.2 V         A27         GND           8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID01         D23         LBUSC10                                                          |                                         | ECLTRG0       | +5 V          | CLK10+        |  |

| 3         ECLTRG1         No Connection         GND           4         GND         A24         -5.2 V           5         MODID12         A25         LBUSC00           6         MODID11         A26         LBUSC01           7         -5.2 V         A27         GND           8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11 </td <td></td> <td>-2 V</td> <td>GND</td> <td></td> |                                         | -2 V          | GND           |               |  |

| 4         GND         A24         -5.2 V           5         MODID12         A25         LBUSC00           6         MODID11         A26         LBUSC01           7         -5.2 V         A27         GND           8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND                                                                  |                                         | ECLTRG1       | No Connection |               |  |

| 5         MODID12         A25         LBUSC00           6         MODID11         A26         LBUSC01           7         -5.2 V         A27         GND           8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*                                                          |                                         | GND           | A24           |               |  |

| 6         MODID11         A26         LBUSC01           7         -5.2 V         A27         GND           8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG5* <td></td> <td>MODID12</td> <td>A25</td> <td></td>     |                                         | MODID12       | A25           |               |  |

| 7         -5.2 V         A27         GND           8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3* <td></td> <td>MODID11</td> <td>A26</td> <td></td>    |                                         | MODID11       | A26           |               |  |

| 8         MODID10         A28         LBUSC02           9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC06           15         MODID05         D18         GND           16         GND         D18         GND           17         MODID04         D19         LBUSC07           18         MODID03         D20         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*<                                                   |                                         | -5.2 V        | A27           |               |  |

| 9         MODID09         A29         LBUSC03           10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG6*         D28         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7                                                   | 8                                       | MODID10       | A28           |               |  |

| 10         GND         A30         GND           11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         No Connection                                                           | 9                                       | MODID09       | A29           |               |  |

| 11         MODID08         A31         LBUSC04           12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31                                                       | 10                                      | GND           | A30           |               |  |

| 12         MODID07         GND         LBUSC05           13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31                                                     | 11                                      | MODID08       | A31           |               |  |

| 13         -5.2 V         +5 V         -2 V           14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         No Connection                                                   |                                         | MODID07       | GND           |               |  |

| 14         MODID06         D16         LBUSC06           15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                             | 13                                      | -5.2 V        | +5 V          |               |  |

| 15         MODID05         D17         LBUSC07           16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                      | 14                                      | MODID06       | D16           |               |  |

| 16         GND         D18         GND           17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                               |                                         | MODID05       | D17           |               |  |

| 17         MODID04         D19         LBUSC08           18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                |                                         | GND           | D18           |               |  |

| 18         MODID03         D20         LBUSC09           19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                         |                                         | MODID04       | D19           |               |  |

| 19         -5.2 V         D21         -5.2 V           20         MODID02         D22         LBUSC10           21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                  | *************************************** | MODID03       | D20           |               |  |

| 21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         | -5.2 V        | D21           |               |  |

| 21         MODID01         D23         LBUSC11           22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         | MODID02       | D22           | LBUSC10       |  |

| 22         GND         GND         GND           23         TTLTRG0*         D24         TTLTRG1*           24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         | MODID01       | D23           |               |  |

| 24         TTLTRG2*         D25         TTLTRG3*           25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |               | GND           |               |  |

| 25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |               | D24           | TTLTRG1*      |  |

| 25         +5 V         D26         GND           26         TTLTRG4*         D27         TTLTRG5*           27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         | TTLTRG2*      | D25           | TTLTRG3*      |  |

| 27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |               | D26           |               |  |

| 27         TTLTRG6*         D28         TTLTRG7*           28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |               | D27           | TTLTRG5*      |  |

| 28         GND         D29         GND           29         No Connection         D30         No Connection           30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |               | D28           |               |  |

| 30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |               | D29           |               |  |

| 30         MODID00         D31         GND           31         GND         GND         No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |               | D30           | No Connection |  |

| 31 GND GND No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |               | D31           |               |  |

| 90   NT C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                         |               | GND           |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32                                      | No Connection | +5 V          | No Connection |  |

Figure 4 - V160 -XY3 Strapping Information

### STRAPPING INFORMATION

Figure 4 shows the factory-configured positions for straps A-E and STP 1,8, the TTL Trigger Line and CLK 10 selections, and the SYSRESE. The configuration is as follows:

- 1.) V160-xyz3 is a Slot 0 device.

- 2.) V160-xyz3 is an Interrupt Handler.

- 3.) Bus Request Level is set to 3.

- 4.) Backplane CLK 10 signal is an output on front panel Clk I/O.

- 5.) Positions 1 through 8 on SW1 are pushed down on top (set to zeros) so V160-xyz3 is at Logical Address zero.

- 6.) V160-xyz3 drives backplane Clk10+/-.

- 7.) TTL Trigger Line 0 is routed to front panel Trig I/O as an output.

- 8.) V160-xyz3 has pull-up enabled for Slot 0 MODID line.

- 9.) V160-xyz3 drives the backplane SYSRESET signal.

Table 7. - Strap Configuration

| T 1 1                      | Table 7 Strap Configuration |                                 |  |  |  |

|----------------------------|-----------------------------|---------------------------------|--|--|--|

| Label Reference Designator |                             | Function                        |  |  |  |

| A                          | STP28                       | * Arbiter Enable                |  |  |  |

| В                          | STP27                       | * Interrupt Handler             |  |  |  |

| C                          | STP24                       | * Slot 0                        |  |  |  |

| D                          | STP25                       |                                 |  |  |  |

| Е                          | STP26                       | Bus Request Level               |  |  |  |

| F                          | STP9                        |                                 |  |  |  |

| G                          | STP10                       |                                 |  |  |  |

| Н                          | STP11                       |                                 |  |  |  |

| J                          | STP12                       |                                 |  |  |  |

| K                          | STP13                       | 1.07                            |  |  |  |

| L                          | STP14                       | * CLK10 +/-                     |  |  |  |

| M                          | STP2                        |                                 |  |  |  |

| N                          | STP4                        | TTL Trigger Line                |  |  |  |

| Р                          | STP3                        |                                 |  |  |  |

| Q                          | STP5                        | TTL Trigger I/O                 |  |  |  |

| /0 0                       | STP7                        | * Slot 0 MODID Line<br>Resistor |  |  |  |

| Label     | Reference Designator | Function                            |  |

|-----------|----------------------|-------------------------------------|--|

| N0 0 STP1 |                      | V160-xyz3 MODID<br>Line             |  |

| CI CO     | STP8                 | CLK10 I/O                           |  |

| DE        | STP15                | * SYSRESET (System<br>Reset Enable) |  |

| V160-xyz3 Strap Descriptions                                                                                                                     |                                                                                                               |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Arbiter Enable                                                                                                                                   | Enables V160-xyz3 to function as the bus arbiter deciding which requester is granted control of the data bus. |  |  |  |

| Interrupt Handler                                                                                                                                | Enables V160-xyz3 to be an Interrupt Handler.                                                                 |  |  |  |

| Slot 0                                                                                                                                           | Enables the V160-xyz3 to be a Slot 0 device.                                                                  |  |  |  |

| Bus Request Level                                                                                                                                | Specifies the bus request level the V160-xyz3 will use when requesting the data bus.                          |  |  |  |

| CLK10 +/- Configures routing for CLK10 +/- to P2 connector.                                                                                      |                                                                                                               |  |  |  |

| TTL Trigger Line Specifies the TTL trigger line to be used in conjunction front panel Trigger I/O.                                               |                                                                                                               |  |  |  |

| TTL Trigger I/O  Determines the direction of the front panel Trigger I/O                                                                         |                                                                                                               |  |  |  |

| Slot 0 MODID                                                                                                                                     | Enables pull-up resistor connected to V160-xyz3 MODID line when used as a Slot 0 device.                      |  |  |  |

| V160-xyz3 MODID Line Used for testing purposes only. Should remain in the fa configured position to connect the MODID line to the More resistor. |                                                                                                               |  |  |  |

| CLK 10 I/O                                                                                                                                       | Configures front panel CLK10 signal as an input or an output.                                                 |  |  |  |

| SYSRESET  Allows an onboard reset signal to be routed to *SYSRESE on backplane.                                                                  |                                                                                                               |  |  |  |

## VXIBUS SLOT 0 CONFIGURATION

The V160-xyz3 is shipped from the factory configured for Slot 0 operation. If is to be installed in any other slot, is must be properly configured before installation.

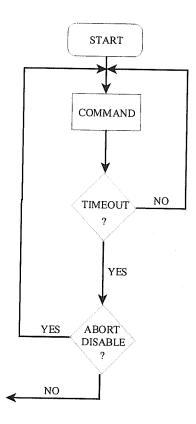

Warning: If the V160-xyz3 is configured for Slot 0 operation, installation in any other slot may result in damage to the V160-xyz3, the Slot 0 device, and the VXIbus backplane.