# **Model V157-AA21**

KineticSystems Power PC Slot0 Controller

User's Manual

October 2008

(C) 2008 Copyright by DynamicSignals LLC Lockport, Illinois All rights reserved

# **Table of Contents**

| INSTALLATION AND SETUP                                        |          |

|---------------------------------------------------------------|----------|

| Logical Address                                               |          |

| CLK10 Signal Generation.                                      |          |

| Installation                                                  |          |

| V157 Front Panel Description                                  |          |

| PMC (PCI Mezzanine Cards)                                     | !        |

| Device Type Register                                          |          |

| Status/Control Register                                       |          |

| Protocol Register                                             |          |

| Write Signal Register                                         | 10       |

| Response Register                                             | 11       |

| Data Low Register                                             |          |

| Suffix High Register                                          |          |

| Suffix Low Register                                           | 18       |

| Serial Number High Register                                   | 18       |

| Serial Number Low Register                                    | 19       |

| Module ID Register                                            | 14       |

| Interrupt Status Register                                     | 14       |

| Interrupt Control Register.                                   | 16       |

| Trigger Interrupt Mask/Trigger Interrupt Source Register      | 17       |

| Trigger Interrupt Source Clear Register                       | 18       |

| Trigger Source Register                                       | 19       |

| Trigger Timer Configuration Register                          | 20       |

| Location Monitor Interrupt Control Register                   | 23       |

| Interrupt Status ID Register                                  | 24       |

| Miscellaneous Control Register                                | 25       |

| Read Signal Register                                          | 26       |

| VXI Transfers                                                 | 26       |

| VXI Triggers                                                  | 27       |

| Synchronous Trigger Example:                                  | 28       |

|                                                               |          |

| APPENDIX A                                                    | 33       |

| V157 Adapter Card Diagram                                     | 33       |

| APPENDIX B                                                    | 35       |

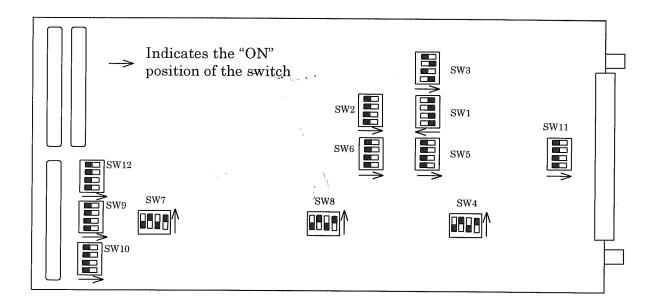

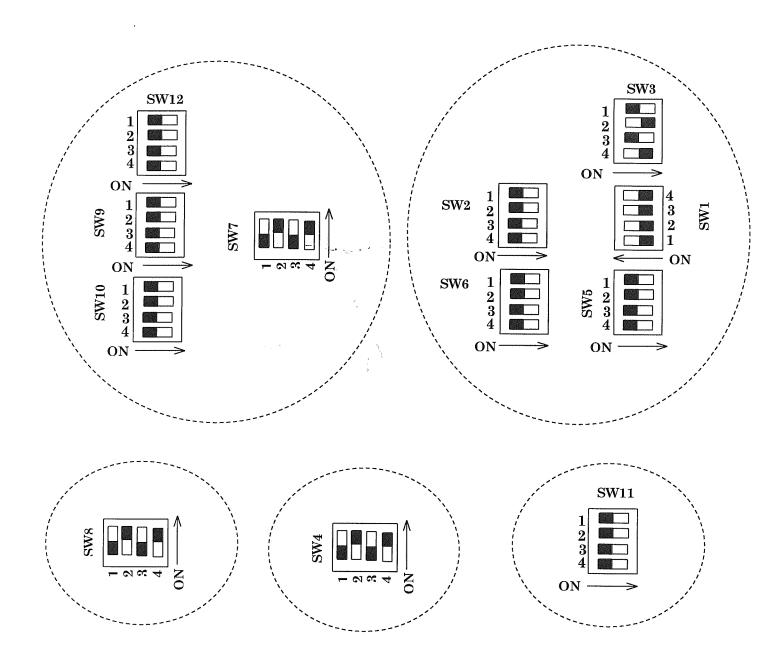

| Single Board Computer (SBC) Switch and Connector Locations    | 25       |

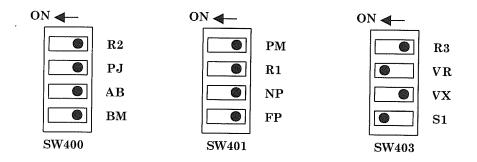

| SW400, SW401 and SW403 Switch Settings                        | 36       |

| SBC Strap Selections                                          |          |

| APPENDIX C                                                    |          |

|                                                               |          |

| VXI P2 Connector Assignments                                  | 38       |

| VXI P2 Connector Assignments  Serial Port(s) Connector Pinout | 39       |

| RS-422 PMC Module Connector Pinout.                           | 40       |

| RS-422 PMC Card Switch Settings                               | 41       |

| Close-Up View of Switch Settings on Serial PMC Card           | 43<br>46 |

|                                                               |          |

#### INSTALLATION AND SETUP

The Model V157 is shipped in an anti-static bag with a styrofoam packing container. Carefully remove the module from its anti-static bag and prepare to set the various options to conform to the operating environment. Make sure that all anti-static precautions are taken to avoid damaging the module.

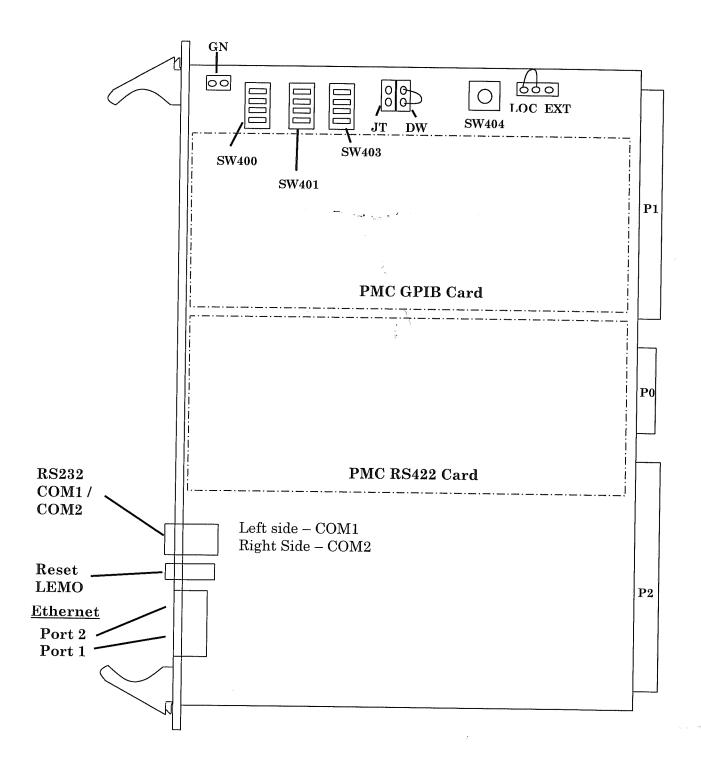

The V157 consists of a VME Single Board Computer (SBC) and a VXIbus adapter unit. Both of these cards require various strap and switch selections to be set before installing the module in the VXI chassis. The following chart shows the strap/switch selections along with their default configurations. If any of the user requirements vary from the default configuration, consult the following sections for changing the parameter. The V157 will be referred to as two components, the V157 adapter and the V157 SBC. Any reference to switch and strap locations on the V157 adapter or V157 SBC can be found in this manual. Additional information concerning operation of the SBC can be obtain from the Creative Electronic Systems (CES) website at <a href="https://www.ces.ch/index.html">www.ces.ch/index.html</a>. The SBC incorporated into the V157 is the RIO4 8072 Entry Level High-Performance Reconfigurable Single Board Computer.

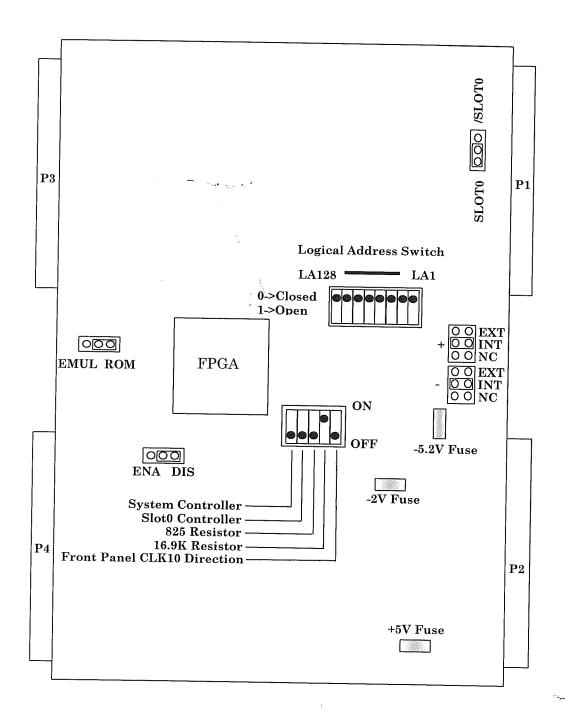

Please refer to Appendix A of this manual for the location of the straps and switches on the V157 adapter and Appendix B for the locations of straps and switches on the V157 SBC.

| Selectable Parameter     | <u>Default Value</u> |

|--------------------------|----------------------|

| V157 Adapter Default     |                      |

| Logical Address          | 0                    |

| System Controller        | Enabled              |

| VXI CLK10 Source         | Internal             |

| V157 SBC Default         |                      |

| P0 JTAG Enable           | Disable              |

| Alternate Boot           | Disable              |

| P0 Mode                  | Disable              |

| NAND Flash Write Protect | Unprotected          |

| NOR Flash Write Protect  | ${f Unprotected}$    |

| VME Reset Mode           | Enable               |

| VME64X                   | Disable              |

| Slot1                    | Enable               |

| Shield Ground            | Disconnect           |

| JTAG Mode                | Disabled             |

| Disable Watchdog         | Disabled             |

| 3.3 Voltage Source       | Local                |

| PMC RS-422 Default       |                      |

| Signaling Protocol       | RS-422               |

| Half-Duplex              | Disabled             |

| Location ID              | Zero                 |

| 3.3 Voltage Source       | Local                |

#### **Logical Address**

The V157 must be located in the Slot0 position as it is a device that can only function as a Slot0 controller. A device that operates as a Slot0 controller must have its Logical Address set to 0.

The V157 contains a set of 8 DIP switches used to set the Logical Address. This set of switches allows a selection of a logical address in the range of 0 to 255. Since the V157 is to be operated as a Slot0 controller, the only Logical Address available is 0 (zero).

A switch that is in the OPEN position yields a bit set to a one. A switch that is in the CLOSED position yields a bit set to a zero. The left-most switch corresponds to Logical Address bit 128 and the right-most switch corresponds to Logical Address bit 1. Please refer to Appendix A for the location and setting of the Logical Address switches. The following diagram shows the bit pattern for the A16 Logical Base Address.

| 15 | 14 | 13  | 12 | 11 | 10. | ~ 9 ´ | 8  | 7  | 6  | 5 | 4 | 3 | 2 | _ 1 | 0 |

|----|----|-----|----|----|-----|-------|----|----|----|---|---|---|---|-----|---|

| 1  | 1  | LA  | LA | LA | LA  | LA    | LA | LA | LA | 0 | 0 | 0 | 0 | 0   | 0 |

|    |    | 128 | 64 | 32 | 16  | , 8   | 4  | 2  | 1  |   |   |   |   |     |   |

Bits 15 and 14 are set to one (VXI defined).

Bits 13 through 6 are user selectable using the Logical Address switches LA128 - LA1. Bits 5 though 0 are set to 0 to indicate the beginning of a 64 byte block.

For statically configured devices, the setting of the Logical Address switches locks the devices' Configuration Registers in A16 address space. Each device has an allocated configuration address space of 64 bytes. The Logical Base Address of a device in A16 address space may then be calculated using the following equation:

A16 Base Address = 0xC000 + (Logical Address \* 64)

For example, the A16 Base Address of a device set for Logical Address 2 is 0xC080. For a device set to Logical Address 2, the following bit pattern is established for the base address.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|---|

| 1  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | l |

### **CLK10 Signal Generation**

The VXIbus CLK10 signal is a 10 Megahertz differential ECL clock driven onto the bus by the Slot0 controller. Since the V157 is used as a Slot0 controller, it must be configured to drive this VXIbus signal. The signal source is generated internally by the V157 and routed out onto the VXIbus.

A set of six straps, located near the P1/P2 connector for VXI, is used to configure the source of the CLK10 signal. This set of straps actually controls the 2 CLK10 signals, +CLK10 and -CLK10. When the straps are installed in the INT (INTERNAL) position, the CLK10 signals are driven by a clock source on the V157. Any other strap selection for this function should be avoided as this would prevent the 10 Mhz clock from reaching the VXIbus.

### Installation

After all the user selectable configuration parameters have been setup, the module may then be inserted into the VXI chassis. In order to use the V157 as a Slot0 controller it *must* be located in the Slot0 position within the chassis. The Slot0 location is slot 0 in the chassis and is the left-most slot.

| CAUTION: | TURN OFF MAINFRAME POWER BEFORE INSERTING OR REMOVING A VXIbus MODULE.                                       |

|----------|--------------------------------------------------------------------------------------------------------------|

| WARNING: | REMEMBER TO REMOVE THE INTERRUPT ACKNOWLEDGE AND BUS GRANT DAISY CHAIN JUMPERS BEFORE INSERTING A VXI MODULE |

The VXIbus backplane must be properly configured before inserting a VXI module and applying power. The Interrupt Acknowledge jumper must be removed from the slot in which the VXI module is to be inserted. The Bus Grant jumpers must also be removed from the slot in which the VXI module is to be inserted. All unoccupied slot locations must have the Interrupt Acknowledge and Bus Grant jumpers installed so that the interrupt and grant continuity is not disrupted by any open slots. When using backplanes that auto-configure, these steps are not necessary since the installation of a VXI module in the chassis makes the required configuration occur.

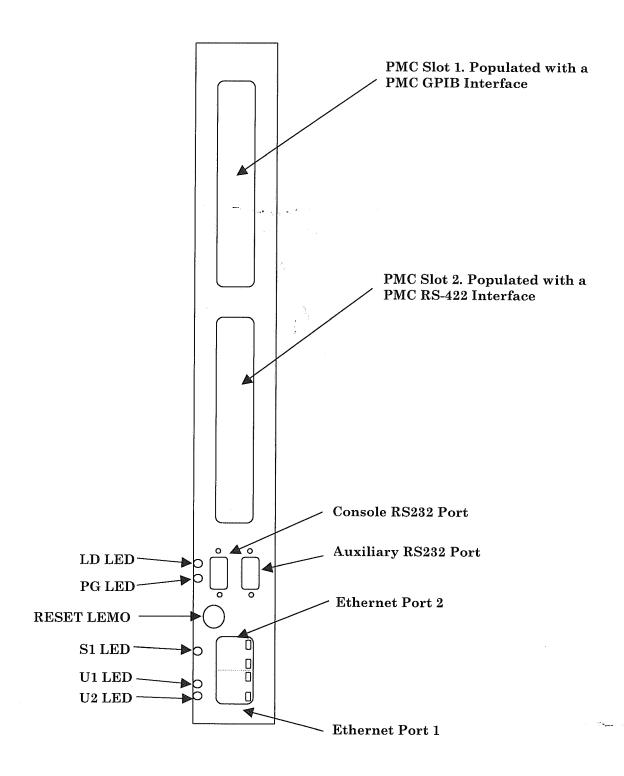

### V157 Front Panel Description

The front panel of the V157 contains all the connections to external peripherals. The table following the diagram details the function of the various indicators.

#### Front Panel Indicators

The following table describes the function of the front panel indicators. The left-most indicators (LED's) can be seen through small holes in the front panel. The LED's associated with each Ethernet connection are just to the right side of the Ethernet connector.

| LED Indicator   | Function          | Color  | Description when LED is illuminated                     |

|-----------------|-------------------|--------|---------------------------------------------------------|

| LD              | FPGA not loaded   | Red    | The FPGA's are not correctly loaded                     |

| PG              | Power Good        | Green  | The power rails for proper operation are within limits. |

| DCM             | DCM Not Locked    | Red    | FPGA's are not DCM locked                               |

| S1              | VME Slot1         | Green  | The V157 is acting as a Slot0 (VME<br>Slot1) Controller |

| Ethernet Port 1 | Ethernet Link     | Green  | Port 1 Link-up                                          |

| Ethernet Port1  | Ethernet Activity | Yellow | Port 1 Activity                                         |

| Ethernet Port 2 | Ethernet Link     | Green  | Port 2 Link-up                                          |

| Ethernet Port2  | Ethernet Activity | Yellow | Port 2 Activity                                         |

| U1              | User Green LED    | Green  | Programmed by the user                                  |

| U2              | User Orange LED   | Orange | Programmed by the user                                  |

### PMC (PCI Mezzanine Cards)

The V157 contains two PMC expansion sites that are populated with PMC cards that extend the functionality of the V157. The top-most PMC site has a GPIB (General Purpose Interface Bus) card installed. This card is a product manufactured by National Instruments. Additional information regarding this interface can be found on the NI website at <a href="https://www.ni.com">www.ni.com</a>.

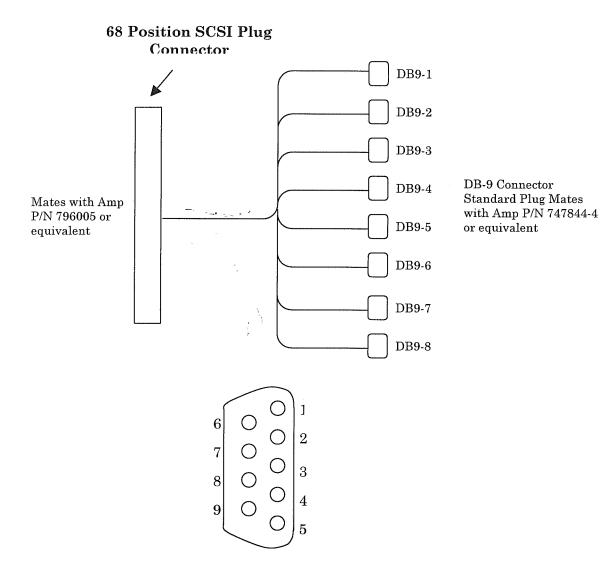

The lower PMC site contains an 8-channel RS422 serial interface PMC card. The 8 channels of serial communication are connected to the PMC card through a 68 position VHDC-style connector. Each of the 8 serial channels utilize RS422 balanced signaling. The signals consist of Transmit (Tx), Receive (Rx), Clear-To-Send (CTS) and Request-To-Send (RTS).

The serial PMC card is a product from Ramix, now distributed by GE Fanuc. The website address to get additional information on this card can be found at <a href="https://www.gefanucembedded.com">www.gefanucembedded.com</a>. The model number of the unit is PMC422/FP.

# VXIbus Configuration Registers and Operational Registers

The following table shows the various registers located in A16 space for the V157 Slot 0 Controller.

| _A16 Offset        | Write Access                                | Read Access                  |

|--------------------|---------------------------------------------|------------------------------|

| 0016               | Logical Address Register                    | Identification               |

| $02_{16}$          | Reserved                                    | Device Type Register         |

| $04_{16}$          | Status/Control Register                     | Status/Control Register      |

| $06_{16}$          | Reserved                                    | Reserved                     |

| $08_{16}$          | Write Signal Register                       | Protocol Register            |

| $0A_{16}$          | Reserved                                    | Response Register            |

| $0\mathrm{C}_{16}$ | Reserved                                    | Reserved                     |

| $0\mathrm{E}_{16}$ | Data Low Register                           | Data Low Register            |

| $10_{16}$          | Reserved                                    | Reserved                     |

| $12_{16}$          | Reserved                                    | Reserved                     |

| $14_{16}$          | Reserved                                    | Reserved                     |

| $16_{16}$          | Reserved                                    | Reserved                     |

| $18_{16}$          | Reserved                                    | Reserved                     |

| $1A_{16}$          | Reserved                                    | Reserved                     |

| $1C_{16}$          | Reserved                                    | Reserved                     |

| $1\mathrm{E}_{16}$ | Reserved                                    | Reserved                     |

| $20_{16}$          | Reserved                                    | Suffix High Register         |

| $22_{16}$          | Reserved                                    | Suffix Low Register          |

| $24_{16}$          | Reserved                                    | Serial Number High Register  |

| $26_{16}$          | Reserved                                    | Serial Number Low Register   |

| $28_{16}$          | Module ID Register                          | Module ID Register           |

| $2A_{16}$          | Reserved                                    | Interrupt Status Register    |

| $2\mathrm{C}_{16}$ | Interrupt Control Register                  | Interrupt Control Register   |

| $2\mathrm{E}_{16}$ | Trigger Interrupt Mask                      | Trigger Interrupt Source     |

| $30_{16}$          | Trigger Interrupt Source Clear              | Reserved                     |

| $32_{16}$          | Trigger Source Register                     | Reserved                     |

| $34_{16}$          | Trigger Timer Configuration Register        | Reserved                     |

| $36_{16}$          | Reserved                                    | Reserved                     |

| $38_{16}$          | Reserved                                    | Reserved                     |

| $3A_{16}$          | Location Monitor Interrupt Control Register | Interrupt Status ID Register |

| $3C_{16}$          | Miscellaneous Control Register              | Read Signal Register         |

| $3\mathrm{E}_{16}$ | Reserved                                    | Version Number Register      |

7:0

128-LA1

### ID/Logical Address Register

The ID/Logical Address Register is a write/read register located at an offset of 00<sub>16</sub> from the A16 Logical Base Address. A read operation to this register returns the Device Class, the addressing modes of the devices' operational registers and the Manufacturers' Identification. A write operation to this register address is typically executed by the Resource Manager during a Dynamic Configuration allocation sequence. During the sequence, the Resource Manager allocates a Logical Address to the V157 by writing a logical address value to the least significant eight bits of this register. The format and bit assignments of this register are shown in the following diagram. Since this register has write-only and read-only bits, two bit patterns are shown.

| On read tra              | nsac                | tions  | :                |            |                            |                        |                |         |        |        |          |        |                      |        | 00     | h                                 |

|--------------------------|---------------------|--------|------------------|------------|----------------------------|------------------------|----------------|---------|--------|--------|----------|--------|----------------------|--------|--------|-----------------------------------|

|                          | 15                  | 14     | 13               | 12         | 11                         | 10                     | 9              | 8       | 7      | 6      | 5        | 4      | 3                    | 2      | 1      | 0                                 |

| Read-only                | 1                   | 0      | 1                | 1          | 1                          | 1                      | 1              | 1       | 0      | 0      | 1        | 0      | 1                    | 0      | 0      | 1                                 |

|                          | Clas<br>Mess<br>Bas | sage   | Addre<br>Mode    |            | <b></b> ,                  | <sup>N</sup> mag• *m.) | , Ki           | neticSy | stems' | Manufa | cturer l | D = F2 | 9 <sub>16</sub> (388 | 31)    |        |                                   |

| Bit(s) Mne<br>15:14 Devi |                     |        |                  | The        | aning<br>ese bit<br>ibinat | s are                  |                |         |        |        |          |        |                      |        |        | This bitevice.                    |

| 13:12 Addr               | ess S               | bpace  |                  | ope<br>V15 | ration                     | ıal re<br>bear         | egiste         | rs. S   | ince   | all th | e con    | ımur   | nicat                | ion re | egiste | e V157's<br>rs of the<br>are both |

| 11:0 Manu                | factu               | rer    |                  |            | s field<br>1(F29           |                        |                |         |        |        | er of    | a VX   | II de                | vice.  | This   | value is                          |

| On write tr              | ansa                | ctions | s:               |            |                            |                        |                |         |        |        |          |        |                      |        | 00     | h                                 |

|                          | 15 1                | 4 1    | 3 12             | 11         | 10                         | 9                      | 8              | 7       | 6      | 5      | 4        |        | 3                    | 2      | 1      | 0                                 |

| Write-only               |                     |        | No               | t Used     |                            |                        |                |         |        |        | Logic    | al Add | Iress                |        |        |                                   |

| ` '                      | n <b>em</b> ot Use  |        | $\mathrm{T}^{1}$ | iese (     | 8 bits                     |                        | anin<br>not us | _       | A wri  | te op  | eratio   | on to  | thes                 | e bits | s has  | no effect                         |

Logical Address 128 through 1 are write-only bits used to set the V157's Logical Address during a Dynamic Configuration cycle executed by the Resource Manager. A Dynamic Configuration sequence is performed on a VXI module when its logical address has been set to  $255 \ (FF_{16})$ .

on the V157.

#### Device Type Register

The Device Type Register is a read-only register located at an offset of  $02_{16}$  from the A16 Logical Base Address of the V157. This register contains the Model Code of the V157. Since the V157 is an A16-only device, the entire 16-bits of this field is used for the Model Code.

Model Codes for VXI Slot0 devices must be in the range of  $00_{16}$  to FF<sub>16</sub>. Model Codes for non-Slot0 devices must be in the range of  $100_{16}$  to FFFF<sub>16</sub>. The V157, as a Slot0 Controller, returns a Model Code of  $57_{16}$ .

The following diagram shows the bit pattern for the Device Type Register for the V157.

#### **Slot0 Configuration:**

|           | 15 | 14 | 13 | 12 | 11 | 10 | · 9 ′ | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|----|----|----|----|----|----|-------|---|---|---|---|---|---|---|---|---|--|

| Read-only | 0  | 0  | 0  | 0  | 0  | 0  | 0     | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |  |

#### Status/Control Register

The Status/Control Register is a write/read register located at an offset of 04<sub>16</sub> from the A16 Logical Base Address of the V157. This register contains write-only, read-only and write/read bits. This register is used to monitor the Module ID VXI signal, control the assertion of SYSFAIL, control Soft Reset, and check the status of the Power-On Self Test. The following two diagrams show the Status/Control Register, one for read accesses and one for write.

04h

For read operations executed to the Status/Control Register:

| Read-Write | 0   | MOD<br>ID* | 1   | 1                   | 1      | 1     | 1     | 1     | 1      | 1    | 1     | 1    | RDY   | PASS   | SYS  | SFT<br>RST |      |

|------------|-----|------------|-----|---------------------|--------|-------|-------|-------|--------|------|-------|------|-------|--------|------|------------|------|

| Bit(s)     | Mn  | emor       | nic |                     |        | M     | leani | ng    |        |      |       |      |       |        |      |            | •    |

| 15         | Not | Used       | -   | This l              | oit is | not u | sed a | nd re | ad as  | a ze | ro.   |      |       |        |      |            |      |

| 14         | МО  | DID*       |     | This line of select | n th   | e VX  | I P2  | conn  | ector. |      |       |      |       |        |      |            |      |

| 13:4       | Not | Used       | •   | These               | bits   | are n | ot us | ed an | ıd rea | d as | ones. |      |       |        |      |            |      |

| 3          | RE  | ADY        |     | Ready               | z is : | a rea | d-onl | v bit | that   | ie e | et to | 9 01 | na in | dicati | na c | 110000     | oful |

| Bit(s) | Mnemonic | Meaning                                                                                                                                                                                                           |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |          | completion of register initialization.                                                                                                                                                                            |

| 2      | PASS     | Pass is a read-only bit that is set to a one when the V157 has completed its power-on self-test without any errors. If an error occurs, this bit is set to a zero and the SYSFAIL signal is asserted by the V157. |

| 1      | SYS INH  | SYSFAIL INHIBIT. Reading this bit as a one indicates that the V157 is prevented from driving the backplane SYSFAIL line.                                                                                          |

| 0      | SFT RST  | SFT RST This bit is read as a one when the V157 has been placed into the Soft Reset state. Writing this register with this bit set to a zero removes the V157 from the soft reset state.                          |

| Write-only | Not Used |                                                                                                                                                                      |     |      |  |  |  |  |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|--|--|--|--|

|            |          | INH                                                                                                                                                                  | RST |      |  |  |  |  |

| Bit(s)     | Mnemonic | Meaning                                                                                                                                                              |     |      |  |  |  |  |

| 15:2       | Not Used | These bits are not used for write operations.                                                                                                                        |     |      |  |  |  |  |

| 1          | SYS INH  | SYSFAIL INHIBIT is a write/read bit used to inhibit to asserting the backplane signal SYSFAIL. Setting this disables the assertion of SYSFAIL and a zero enables the | bit | to a |  |  |  |  |

| 0          | SFT RST  | SOFT RESET is a write/read bit used to reset the V157 bit to a one places the V157 in the soft reset state and w to a zero removes the V157 from the reset state.    |     |      |  |  |  |  |

04h

For write operations executed to the Status/Control Register:

### **Protocol Register**

The Protocol Register is a read-only register located at an offset of  $08_{16}$  from the A16 Logical Base Address of the V157. The Protocol Register is accessed by executing a read to this address location and the Signal Register is accessed by writing to this location. The Protocol Register is used to define the communication capabilities of the Message Based Device. The following diagram shows the bit layout of the Protocol Register for the V157.

|           |       |              |       |                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |                           |                       |                        |                         |                           |                       |                   |                            |                         | 08                      | h                                                |  |

|-----------|-------|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------|-----------------------|------------------------|-------------------------|---------------------------|-----------------------|-------------------|----------------------------|-------------------------|-------------------------|--------------------------------------------------|--|

|           | 15    | 14           | 13    | 12                                                                                                                                                                                                                                                                                                                                                                                                                       | 11                      | 10                        | 9                     | 8                      | 7                       | 6                         | 5                     | 4                 | 3                          | 2                       | 1                       | 0                                                |  |

| Read-only | CMDR* | SGNL<br>REG* | MSTR* | INTR                                                                                                                                                                                                                                                                                                                                                                                                                     | FHS*                    | SHR<br>MEM*               | 1                     | 1                      | 1                       | 1                         | 1                     | 1                 | 1                          | 1                       | 1                       | 1                                                |  |

|           |       | REG          |       |                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | MEM.                      |                       | l                      |                         | <u> </u>                  |                       |                   | <u> </u>                   | <u> </u>                | Ĺ                       |                                                  |  |

| Bit(s)    |       | emon         | ic    |                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |                           | <b>Iean</b>           |                        |                         |                           |                       |                   |                            |                         |                         |                                                  |  |

| 15        | CMI   | DR*          |       | only<br>locat<br>Serv                                                                                                                                                                                                                                                                                                                                                                                                    | capa<br>ion ii<br>ant N | ble of<br>ndicat<br>Iessa | Mes<br>tes tl<br>ge B | sage<br>nat th<br>ased | Base<br>ie dev<br>funct | d Ser<br>vice is<br>ions. | vant<br>s capa<br>The | funct<br>able c   | tions.<br>of bot<br>7 sets | A ze<br>h Cou<br>s this | ero in<br>mmar<br>bit t | vice that<br>a this bit<br>ader and<br>to a zero |  |

| 14        | SGN   | IL-RF        | EG*   | SIGNAL REGISTER is a read-only bit that is set to a one for a device that does not contain a Signal Register. Devices that contain a Signal Register set this bit to a zero. Since the V157 contains a functional Signal Register, this bit is set to a zero.  MASTER is a read-only bit that is set to a one for devices that do not have VMEbus mastering capability. A zero for this bit location                     |                         |                           |                       |                        |                         |                           |                       |                   |                            |                         |                         |                                                  |  |

| 13        | MST   | TR*          |       | Signal Register, this bit is set to a zero.  MASTER is a read-only bit that is set to a one for devices that do no have VMEbus mastering capability. A zero for this bit location indicates the device has the ability to become a VMEbus master. The V157 has VMEbus mastering capability and sets this bit to a zero.                                                                                                  |                         |                           |                       |                        |                         |                           |                       |                   |                            |                         |                         |                                                  |  |

| 12        | INT   | R            |       | indicates the device has the ability to become a VMEbus master. The V157 has VMEbus mastering capability and sets this bit to a zero.  INTERRUPTER is a read-only bit that indicates whether the device can generate interrupts. A zero in this bit location indicates no interrupting ability and a one indicates that the device can generate interrupts. The V157 can generate interrupts and sets this bit to a one. |                         |                           |                       |                        |                         |                           |                       |                   |                            |                         |                         |                                                  |  |

| 11        | FHS   | *FAS         |       | interrupts. The V157 can generate interrupts and sets this bit to                                                                                                                                                                                                                                                                                                                                                        |                         |                           |                       |                        |                         |                           |                       |                   |                            |                         |                         |                                                  |  |

| 10        | SHR   | MEN          |       | imple<br>share                                                                                                                                                                                                                                                                                                                                                                                                           | ement<br>ed me          | s sha<br>mory             | red r                 | nemo<br>uppor          | ry. <i>A</i><br>ted a   | Azero<br>Inda             | in thone i            | nis bii<br>indica | t loca<br>ites t           | tion i<br>hat i         | ndica<br>t is n         | a device<br>tes that<br>ot. The<br>a one.        |  |

| 9:0       | Not I | Used         | i     | These                                                                                                                                                                                                                                                                                                                                                                                                                    | e bits                  | are n                     | ot us                 | ed by                  | the '                   | V157                      | and r                 | returr            | ned as                     | s ones                  | €.                      |                                                  |  |

# Write Signal Register

The Write Signal Register is a write-only register located at an offset of  $08_{16}$  from the A16. Logical Base Address of the V157. A write operation to this register address accesses the Signal Register. This register is used for device to device signaling. This register can be read at offset  $3C_{16}$  in A16 address space. A signal received from a device contains the devices'

Logical Address along with a field for device specific information. There are two different formats for the Signal Register, depending on the value of the most significant bit (bit 15). The following two diagrams show the various formats.

|            | ,  |    |    |    |         |    |   |   |   |   |   |         |        |   | 08   | h |

|------------|----|----|----|----|---------|----|---|---|---|---|---|---------|--------|---|------|---|

|            | 15 | 14 | 13 | 12 | 11      | 10 | 9 | 8 | 7 | 6 | 5 | 4       | 3      | 2 | 1    | 0 |

| Write-only | 0  |    |    | F  | Respons | se |   |   |   |   | [ | _ogical | Addres | s | ···· |   |

|            |    |    |    |    |         |    |   |   |   |   |   |         |        |   | 08   | h |

| p          | 15 | 14 | 13 | 12 | 11      | 10 | 9 | 8 | 7 | 6 | 5 | 4       | 3      | 2 | 1    | 0 |

| Write-only | 1  |    |    |    | Event   |    |   |   |   |   | L | _ogical | Addres | s |      |   |

The fields shown for the two Signal Register patterns are as follows:

Response: This field reflects bits 14 through 8 of the device's Response Register.

Event: This field reflects the event associated with the signal.

Logical Address: This field reflects the Logical Address of the device generating the signal.

### Response Register

The Response Register is a read-only register located at an offset of  $0A_{16}$  from the A16 Logical Base Address of the V157. This register is used to return the status of a device's communication registers and their associated functions. The following diagram shows the bit layout for the Response Register on the V157.

0Ah

|              |   | ,              |             |                                                               |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |                      |       |                |                  | _              | _              | •              | •              |

|--------------|---|----------------|-------------|---------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|----------------------|-------|----------------|------------------|----------------|----------------|----------------|----------------|

| Read-only    | 0 | 1              | 0           | 0                                                             | ERR*         | READ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | WRT             | 1               | 1                    | 1     | 1              | 1                | 1              | 1              | 1              | 1              |

|              |   |                |             |                                                               |              | RDY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RDY             |                 |                      |       |                |                  |                |                |                |                |

| Bit(s)<br>15 |   | Inem<br>lot Us | onic<br>sed |                                                               | $\mathbf{T}$ | his bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t is n          |                 | <b>anin</b><br>ed an | _     | d as a         | ı zero           | •              |                |                |                |

| 14           | N | lot Us         | sed         | This bit is not used and read as a one.                       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |                      |       |                |                  |                |                |                |                |

| 13:12        | N | lot Us         | sed         | These two bits are not used by the V157 and returned a zeros. |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |                      |       |                |                  |                |                |                |                |

| 11           | Е | RR             |             |                                                               |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |                      |       |                |                  |                |                |                |                |

| 10           | R | EAD            | RDY         |                                                               | th<br>Tl     | EAD at the bis since the contract the contra | e der<br>t is s | vice's<br>et to | Data<br>a one        | a Reg | ister<br>execu | (s) co<br>ting a | ntair<br>a wri | data<br>te ope | a to<br>eratio | be-re<br>on to |

| Bit(s) | Mnemonic | Meaning bit set to a one. After the READ READY bit has been set, it is cleared when the Data Low Register is read.                                                                                                                                                                                                                         |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9      | WRT RDY  | WRITE READY is a read-only bit that is set to a one indicating that the device is ready for data transfers to its Data Register(s). This bit is set to a one by executing a write to the Miscellaneous Control Register with the SET WRITE READY bit set to a one. After the Data Low Register is written, the WRITE READY bit is cleared. |

| 8:0    | Not Used | These bits are not used by the V157 and read as ones.                                                                                                                                                                                                                                                                                      |

### **Data Low Register**

The Data Low Register is a write/read register located at an offset of 0E<sub>16</sub> from the A16 Logical Base Address of the V157. This register is used communicate data between two Message Based Devices. Accessing this register causes the appropriate flags to be set/cleared in the Response Register. Please refer to the Response Register for additional information.

The following diagram shows the bit pattern for the Data Low Register.

|            |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 0E | ìh |

|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|            | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Read-Write | DL |

|            | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 1  |

Bit(s) Mnemonic 15:0 W/R15:0

Meaning

WRITE/READ DATA 15 through 0 are write/read bits used

to communicate data between two Message Based Devices.

#### Suffix High Register

The Suffix High Register is a read-only register located at an offset of 20<sub>16</sub> from the A16 Logical Base Address of the V157. This register is used in combination with the Suffix Low Register to determine the module model number suffix. The Suffix High Register contains the first two ASCII characters of the suffix and the Suffix Low Register contains the last two characters. The suffix shown is for the V157-AA21 module.

The bit pattern for the Suffix High Register is as follows:

|           |    |    |    |    |    |    |   |   |   |   |   |   |   |   | 20 | h |  |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|----|---|--|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |  |

| Read-only | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0  | 1 |  |

# **Suffix Low Register**

The Module Suffix Low Register is a read-only register located at an offset of 22<sub>16</sub> from the A16 Logical Base Address of the V157. This register is used in combination with the Suffix High Register to determine the module model number suffix. The Suffix Low Register contains the last two ASCII characters of the suffix and the Suffix High Register contains the first two characters. The suffix shown is for the V157-AA21 module.

The bit pattern for the Suffix Low Register is as follows:

|           |    |    |    |    |    |    |   |   |   |   |   |   |   |   | 22 | h |

|-----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|----|---|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

| Read-only | 0  | 0  | 1  | 1  | 0  | 0  | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0  | 1 |

### Serial Number High Register\_

The Serial Number High Register is a read-only register located at an offset of 24<sub>16</sub> from the A16 Logical Base Address of the V157. This register is used in conjunction with the Serial Number Low Register to define the serial number of the V157. The following diagram shows the bit pattern of the Serial Number High Register.

|           |    |    |    |    | . * |    |     | 1  |    |    |    |    |    |    | 24 | h  |

|-----------|----|----|----|----|-----|----|-----|----|----|----|----|----|----|----|----|----|

|           | 15 | 14 | 13 | 12 | 11  | 10 | 9 🖟 | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Read-Only | SN | SN | SN | SN | SN  | SN | SN  | SN | SN | SN | SN | SN | SN | SN | SN | SN |

|           | 31 | 30 | 29 | 28 | 27  | 26 | 25  | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

#### Serial Number Low Register

The Serial Number Low Register is a read-only register located at an offset of 26<sub>16</sub> from the A16 Logical Base Address of the V157. This register is used in conjunction with the Serial Number High Register to define the serial number of the V157. The following diagram shows the bit pattern of the Serial Number Low Register.

|           |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 26 | h  |

|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Read-Only | SN |

|           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

# Module ID Register

The Module ID Register is a write/read register located at an offset of 28<sub>16</sub> from the A16 Logical Base Address of the V157. The Module ID Register is used to control the MODID geographic addressing lines on the VXI P2 connector. Each of the 13 slots of a VXI chassis has an individual line that can be asserted and monitored through the Module ID Register. Before any of the MODID lines can be asserted by the V157, the Output Enable bit (bit 13) of this register

must be set to a one. When the outputs are enabled, setting a MODID bit location to a one asserts the corresponding MODID signal.

The data read from this register does not necessarily reflect the data written. Instead, a read of this register returns the actual state of the MODID signals on the VXI backplane.

The following diagram shows the bit pattern for the Module ID Register.

|                 |    |                       |                     |     |                                                                                                                                                                                |        |       |     |       |     |       |        |       |     | 28  | $\mathbf{h}$ |   |

|-----------------|----|-----------------------|---------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-----|-------|-----|-------|--------|-------|-----|-----|--------------|---|

|                 | 15 | 14                    | 13                  | 12  | 11                                                                                                                                                                             | 10     | 9     | 8   | 7     | 6   | 5     | 4      | 3     | 2   | 1   | 0            |   |

| Read-Write      | 0  | 0                     | MID                 | MID | MID                                                                                                                                                                            | MID    | MID   | MID | MID   | MID | MID   | MID    | MID   | MID | MID | MID          |   |

|                 |    |                       | ENA                 | 12  | 11                                                                                                                                                                             | 10     | 9     | 8   | 7     | 6   | 5     | 4      | 3     | 2   | 1   | 0            |   |

| Bit(s)<br>15:14 |    | <b>Mne</b> i<br>Not U | <b>moni</b><br>Jsed | c   | Meaning These bits are not used and read as ones.                                                                                                                              |        |       |     |       |     |       |        |       |     |     |              | • |

| 13              | Ī  | MID :                 | ENA                 |     | MODID OUTPUT ENABLE is a write/read bit used to enable/disable the V157 from driving the MODID signals Setting this bit to a one enables the drivers and a zero disables them. |        |       |     |       |     |       |        |       |     |     |              |   |

| 12:0            | ]  | MID1                  | 2:0                 |     | mon                                                                                                                                                                            | itor t | he 13 | MO: | DID 8 |     | ls. V | Vritin | g a b |     |     | sert a       |   |

# **Interrupt Status Register**

The Interrupt Status Register is a read-only register located at an offset of  $2A_{16}$  from the A16 Logical Base Address of the V157. The contents of this register are enabled onto the VMEbus during an interrupt acknowledge cycle. This register contains the Logical Address of the V157 in the lower 8-bits of the register and the upper 8-bits contains the cause/status of the interrupt. The lower 8-bits of this register return the Logical Address of the V157 only for interrupt acknowledges cycles. An I/O read of this field returns all 8-bits set to ones.

The V157 has two interrupt sources. One of the sources is from a pre-selected VXI Trigger input and the other source is from Location Monitors. The VXI interrupt sources are enabled through the Trigger Interrupt Mask Register located at offset  $2E_{16}$ . The Location Monitor interrupt sources are enabled through the Location Monitor Interrupt Control Register located at an offset of  $3A_{16}$ . These two registers must be appropriately enabled before the V157 can generate an interrupt source. The interrupt source(s) may then generate a VXI interrupt request when interrupts are enabled in the Interrupt Control Register located at an offset of  $2C_{16}$ .

The interrupt acknowledge (IACK) cycle executed by the Interrupt Handler reads a 16-bit value from the V157. The lower 8-bits of this data reflects the Logical Address of the device

generating the interrupt. The upper 8-bits reflects the cause of the interrupt. Of the upper 8-bits, only 2 of them are used by the V157 to relay the cause of the interrupt. Once an interrupt acknowledges cycle occurs, the interrupt source bits that were set in this register when the interrupt vector was read are reset to zero. This will also occur when the Interrupt Status Register is read.

The format of the Interrupt Status Register is as follows:

|                           |    |              |     |    | 11 10 9 8 7 6 5 4 3 2                                                                                                                                                                                                                                                                                                                                                                            |       |       |               |                        |        |       |        |       | 2A                          | h              |                |                   |

|---------------------------|----|--------------|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------|------------------------|--------|-------|--------|-------|-----------------------------|----------------|----------------|-------------------|

| OUR BESTEVANTA CONTRACTOR | 15 | 14           | 13  | 12 | 11                                                                                                                                                                                                                                                                                                                                                                                               | 10    | 9     | 8             | 7                      | 6      | 5     | 4      | 3     | 2                           | 1              | 0              |                   |

| Read-Only                 | 0  | 0            | 0   | 0  | 0                                                                                                                                                                                                                                                                                                                                                                                                | 0     | LOC   | TRG           | LA                     | LA     | LA    | LA     | LA    | LA                          | LA             | LA             |                   |

|                           |    |              |     |    |                                                                                                                                                                                                                                                                                                                                                                                                  |       | MON   | IN            | 128                    | 64     | 32    | 16     | 8     | 4                           | 2              | 1              |                   |

| Bit(s)<br>15:10           |    | Mne<br>Not U |     | ic |                                                                                                                                                                                                                                                                                                                                                                                                  |       |       | Mean<br>not ι |                        | and re | ead a | s zero | os.   |                             |                |                | •                 |

| 9                         |    | LOC          | MON | I  | These bits are not used and read as zeros.  LOCATION MONITOR INTERRUPT SOURCE is a read-and-clear bit that is set when an interrupt source is generated by one of the Location Monitor Interrupts enabled in the Location Monitor Interrupt Control Register. To find out the actual cause of the location monitor interrupt, the Location Monitor Interrupt Control Register must be consulted. |       |       |               |                        |        |       |        |       |                             |                |                |                   |

| 8                         |    | TRG          | IN  |    | Monitor Interrupt Control Register. To find out the actual cause of the location monitor interrupt, the Location Monitor                                                                                                                                                                                                                                                                         |       |       |               |                        |        |       |        |       |                             |                |                | the<br>upt<br>out |

| 7:0                       |    | LA12         | 8:1 |    | of th                                                                                                                                                                                                                                                                                                                                                                                            | ie V1 | 57 du | ring          | SS 12<br>an in<br>bits | terru  | pt ac | know   | ledge | ne Lo <sub>l</sub><br>cycle | gical<br>to th | Addro<br>ne V1 | ess<br>57.        |

# **Interrupt Control Register**

The Interrupt Control Register is a write/read register located at an offset  $2C_{16}$  from the A16 Logical Base Address of the V157. This register is used to configure the V157 for interrupt sourcing. The Interrupt Request Level, Interrupt Enable, and Interrupt Source Mask are contained in this register.

The format and description of the Interrupt Control Register are shown in the following diagram.

|                |    |                       |                      |    |                                                                                                                                                                                                                                                                                                                                                                                                   |       |        | 20   | Ch   |        |       |       |     |   |   |   |           |

|----------------|----|-----------------------|----------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|------|------|--------|-------|-------|-----|---|---|---|-----------|