# KineticSystems Company, LLC Preston Scientific PRESYS 1000 User's Manual

June, 2004

(C) 2004 Copyright by KineticSystems Company, LLC Lockport, Illinois All rights reserved

#### PRESYS 1000 SYSTEMS

#### USER MANUAL

SECTION 1: PRESYS 1000 BROCHURE

SECTION 2: CHAN\_ID DEFINITION

CHANNEL IDENTIFICATION (FIGURE 3-9A)

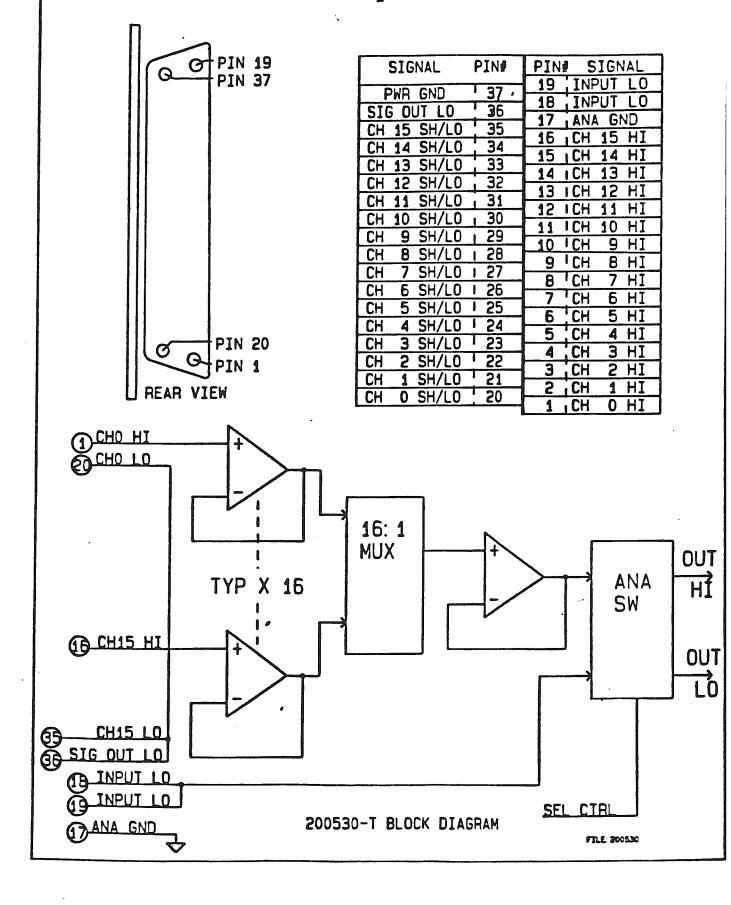

GENERAL BLOCK DIAGRAM

PRESYS BUS/BACKPLANE OVERVIEW

SECTION 3: INSTALLATION

SECTION 4: FRONT PANEL DRAWING

FRONT PANEL QUICK REFERENCE PROGRAMMING GUIDE

FRONT PANEL CONTROL PROGRAMMING

ERROR CODE MESSAGES

SECTION 5: INTERPACE DESCRIPTION

SECTION 6: REMOTE PROGRAMMING DESCRIPTION

SECTION 7: USER CONNECTIONS

SECTION 8: APPLICATION NOTES

# PRESYS 1000

Analog and Digital Input and Output Data Processing Sub-System

**PRESTYS** 1000 the data processing sub-system that combines multi-channel A/D Conversion, D/A Conversion, Digital Input and Output multiplexing all in ONE instrumentation package.

# PRESYS 1000

PRESYS 1000, Preston's newest data conversion system is organized as an "Analog and Digital, Input and Output" Data Processing Sub-System that combines multi channel A/D Conversion, D/A Conversion, Digital Input and Output multiplexing all in one easily interfaced instrumentation package.

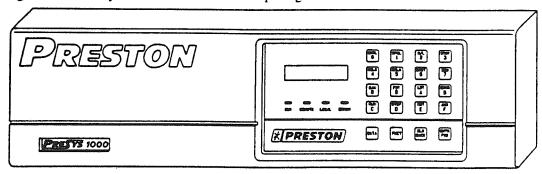

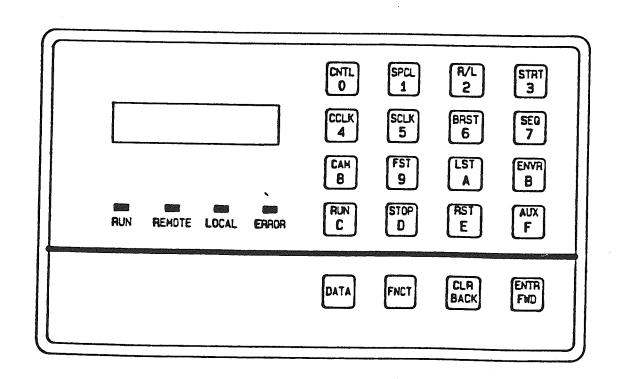

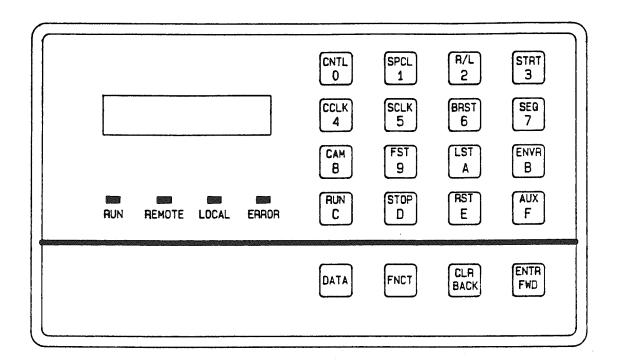

PRESYS 1000 Control Panel

The basic system includes space for high-speed A/D Converter, combined input/output DATA BUS featuring Analog Bus structure for Analog inputs and Digital Bus structure for Digital Inputs and Digital Outputs (Memory expansion, multiple computer interfaces and D/A Converters). Further the basic PRESYS 1000 System Chassis includes the UPC controller, 30K word channel address memory, 128K FIFO memory, basic computer interface, front panel control system and separate power supplies for Analog and Digital modules.

PRESYS 1000 Systems provide easily configured Analog and Digital Data Acquisition; Analog and Digital data Output; all in one compact Instrumentation package. System interface options are offered for most micro, mini and super-mini computers and Array Processors with the possibility to interface one or more computers for control and/or simultaneous data Output.

PRESYS 1000 systems will offer most Preston's existing GM, EM, LC, SDAC Series, A/D and D/A conversion channels. Most circuit boards are being repackaged to fit the PRESYS 1000 BUS concept therefore the multiplexer, amplifier, Sample-and-Hold, DAC's and filter plug-in cards cannot be moved from the existing GM systems to PRESYS 1000 systems.

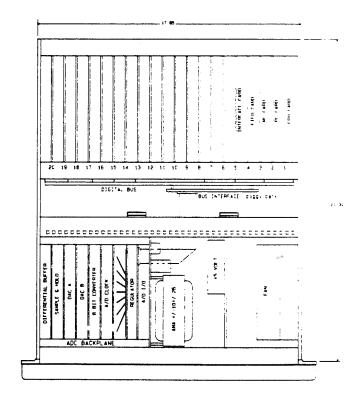

The PRESYS 1000 Chassis includes UPC controller, ADC backplane and the Input/Output backplane. There is also an expander chassis that can be configured with Bus/Address expansion electronics to expand PRESYS 1000 Input/Output channel capability.

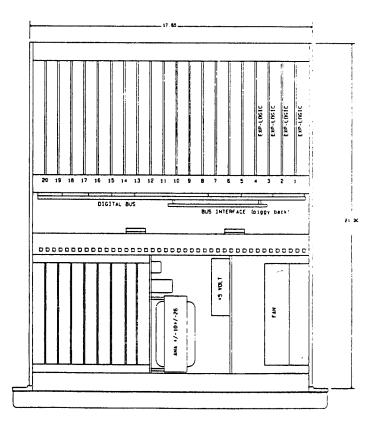

PRESYS 1000 Master Chassis

PRESYS 1000 Basic Chassis has space for 15 card modules which contain either Analog Input Channels, Digital Input Channels and/or Digital and Analog Output Channels (D/A Converters).

This same Card space will also accept other System functions...additional Computer Interfaces, FIFO expansion, and Chassis expansion electronics (the logic necessary to attach the PRESYS 1000 Expansion Chassis).

Any of these 15 Card Slots will accept any of the following Input or Output Channels or System Control Functions...

Analog Multiplexer 16 Channels/Module, Sim Sample-and-Hold 8 Channels/Module, Digital Inputs 16 Bits/Module, Digital Outputs 16 Bits/Module, Analog Outputs 1-4 Channels/Module, FIFO Buffer 128K to 1 Meg/Module, Computer Interface 1 or 2 Modules/Interface, and Bus Expansion 2 to 4 Modules/Chassis.

PRESYS 1000 Expansion Chassis has 16 Card Slots available to accept either Analog Input Channels, Digital Input Channels and/or Digital and Analog Output Channels. Any of these 16 Card Slots will accept any of the input or output channels as previously defined. There are 4 additional Card Slots that are dedicated to service bus expansion needs for attaching the PRESYS 1000 Expansion Chassis to the PRESYS 1000 Basic System Chassis.

### PRESTYS 1000 Basic System

#### STANDARD CONFIGURATION

Master Chassis has 15 Card Slots for accepting Analog and Digital, Inputs and Outputs as noted here-in.

#### ANALOG INPUTS...

PMX Series Multiplexer PSH8 Sample-and Hold Amp-Filter-Mux Filter-MUX

#### DIGITAL MODULES AND ANALOG OUTPUTS...

PDAC Series D/A Converters (Choice of 7 models) FIFO Memories Digital Inputs Digital Outputs Computer Interfaces

#### PRESYS 1000 A/D CONVERSION(\*)

PAD 15-1 A/D Converter, 15 Bits @ 1 MHz PAD 15-2 A/D Converter, 15 Bits @ 500 kHz PAD 15-3 A/D Converter, 15 Bits @ 307 kHz PAD 16-3 A/D Converter, 16 Bits @ 307 kHz PAD 13-1 A/D Converter, 13 Bits @ 1 MHz PAD 13-2 A/D Converter, 13 Bits @ 500 kHz PAD 13-3 A/D Converter, 13 Bits @ 307 kHz

(\*) Plugs into dedicated ADC Backplane as shown in the PRESYS 1000 Master Chassis drawing.

#### OTHER PRESYS 1000 FEATURES...

The PRESYS 1000 Bus system was created to eliminate custom chassis configuration, custom backplanes and custom wiring. This is achieved by bringing all data and control signals to a Mecca type Bus. The Bus uses a 96 pin DIN connector and will incorporate many of the functions of Preston's older MCLS Control System while providing for custom design implementations as well.

Although the Bus concept has been the primary design objective of the PRESYS 1000 System, the standardized form factors, off the shelf power supplies, accessories and modularity of components have been just as important. The connectors and chassis are all Euro-card form factor. PRESYS 1000 Systems have two Power Supplies, one for Analog and one for Digital. The initial PRESYS 1000 Systems utilize existing GM Series ADC with backplane which is mounted in the front row of the chassis. The back of the chassis will house the MUX, other Analog Input Modules, the interface cards and digital Input/Output modules. The ADC and power supplies occupy the front row. There are three dedicated card slots in the rear row that have electronics associated with UPC control. Two additional card slots are required for a simple type computer interface (i.e. DRQ3B, 12006A or DR11W, etc...) and FIFO Memory (16 Bit X 128K).

The remaining 15 Card Slots in the rear row are configured to accept Input/Output channels.

# PRESYS 1000

The PRESYS 1000 Basic Chassis is 5.22 inches high and mounts in standard 19 inch cabinets. Cooling is provided to the chassis by drawing air in from the top and back while exhausting air out the side (there will be 1 small AC fan). A center plentum will allow for improved air circulation and will maintain a constant air flow over the ADC regardless of board configuration. The total wiring of the system comprise mostly power and ground with perhaps 3 or 4 header cable interconnections, thus eliminating special custom inter-module wiring.

The front panel has a hex pad and some control to provide the ability to select hex, decimal, octal or binary display and local verse remote control. The display will be an LCD type with alpha-numeric capability. There is a front panel indication of remote or local operation RUN or ERROR conditions. In addition to displaying data in hex and decimal (counts) the output of converted analog data can be displayed in volts. Binary display of output data is not available.

The basic control electronics is configured using PLD modules mounted on printed circuit cards and includes most of the functions of the existing MCLS Control Systems.

The UPC Controller will also manage the internal Input/Output Bus structures in determining channel type, system configurations and channel sequencing.

Interfacing to PRESYS 1000 will actually be very similar to the existing GM-System interface except much easier to change interface configurations. The main virtue of PRESYS 1000 system is to allow much easier integration of a variety of Analog and Digital Channels with multiple computer interfaces, expanded FIFO's, etc. plus the ability to easily reconfigure those systems by adding or exchanging either Input or Output modules.

PRESYS 1000 can be totally reconfigured in a matter of minutes. Change interfaces, add input or output channels, even add expansion chassis all in less than 45 minutes.

This data sheet covers only the beginning of the PRESYS 1000 story...more comes later in updates and supplements to this brochure.

**EXPANDER CHASSIS**

Preston Scientific

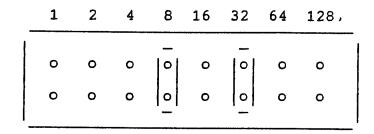

Each PRESYS system must contain one Master chassis, and may include one or more Expansion chassis. When ac power is applied, the system scans the cards installed for type and location. The resulting information is used to generate a channel numbering table which is stored in a non-volatile memory. FIGURE 3-9A defines the standard numbering sequence.

The following list summarizes the number of channels on most standard cards.

- \* 16 channel analog multiplexers

- \* 8 channel simultaneous sample-and-holds

- \* 4 channel simultaneous sample-and-hold

- \* 4 channel analog output card

- \* 8 channel analog output card

- \* 2 channel programmable gain amplifier

- \* 1 channel (16 line) digital input

- \* 1 channel (16 line) digital output

- \* 2 channel (32 line) digital input

- \* 2 channel (32 line) digital output

- \* 1 channel counter (16 bit)

- \* 2 channel counter (32 bit)

As indicated in FIGURE 3-9, numbering usually begins in the Master chassis. The following configurations, indicate channel numbering for systems as delivered. Note that if cards with different locations are switched, channel numbering for all succeeding cards will be changed when the system is next powered "ON".

Channel numbering begins with 0 in the highest numbered slot containing a user I/O card. Empty slots are ignored. Interfaces, sub-multiplexers, and control cards are also ignored

#### REAR OF CHASSIS

#### TOP VIEW

| granese en en en en |       |        |                                         |                                        | <i></i> |

|---------------------|-------|--------|-----------------------------------------|----------------------------------------|---------|

| 20                  |       |        |                                         |                                        |         |

| 19                  |       |        |                                         |                                        |         |

| 18                  |       |        |                                         |                                        |         |

| 17                  |       |        |                                         |                                        |         |

| 16                  |       |        |                                         |                                        |         |

| 15                  |       |        | *************************************** |                                        |         |

| 14                  |       |        |                                         |                                        |         |

| 13                  |       |        | · · · · · · · · · · · · · · · · · · ·   |                                        |         |

| 12                  |       |        |                                         |                                        |         |

| 11                  |       |        |                                         | ······································ |         |

| 10                  |       |        |                                         |                                        |         |

| 9                   |       |        |                                         |                                        |         |

| 8                   |       |        |                                         |                                        |         |

| 7                   |       |        |                                         |                                        |         |

| 6                   |       |        |                                         |                                        |         |

| 5                   |       |        |                                         | <u></u>                                |         |

| 4                   |       |        |                                         |                                        |         |

| 3                   |       |        | <u></u>                                 |                                        |         |

| 2                   |       |        |                                         |                                        |         |

| 1                   |       |        |                                         |                                        |         |

| AC                  | POHER | SW1TCH | WIRING                                  |                                        |         |

PRESYS 1000 & 4000 CHASSIS BACK ROW

#### NOTE:

THE SYSTEM DETECTS THE NUMBER OF CHANNELS ON CARDS INSTALLED, WHEN POWERED ON.

IN PRESYS 1000 SYSTEMS, CHANNEL ADDRESSES BEING WITH 0 ON CARD IN HIGHEST NUMBERED SLOT & INCREASE AS SLOT NUMBERS DECREASE.

IN PRESYS 4000 SYSTEMS, CHANNEL ADDRESSES BEGIN WITH 0 ON CARD IN LOWEST NUMBERED SLOT AND INCREASE AS SLOT NUMBERS INCREASE.

ADDRESSES ARE NOT ASSIGNED TO UNUSED SLOTS.

IN MULTIPLE CHASSIS SYSTEMS, CHANNEL 0 USUALLY BEGINS IN THE MASTER CHASSIS.

#### PRESYS 1000 SYSTEM EXAMPLE

| SLOT | CARD INSTALLED | ADDRESSES           |

|------|----------------|---------------------|

| 20   | 16 CHANNEL MUX | 0 - 15              |

| 19   | 8 CHANNEL S/H  | 16 - 23             |

| 18   | EMPTY          |                     |

| 17   | 2 CHANNEL D/A  | 2 <del>1</del> - 25 |

#### PRESYS 4000 SYSTEM EXAMPLE

| SLOT | CARD INSTALLED | ADDRESSES |

|------|----------------|-----------|

| 20   | 4 CHANNEL ADC  | 4 - 7     |

| 19   | 2 CHANNEL ADC  | 2 - 3     |

| 18   | EMPTY          |           |

| 17   | 2 CHANNEL ADC  | 0 - 1     |

FIGURE 3-9A

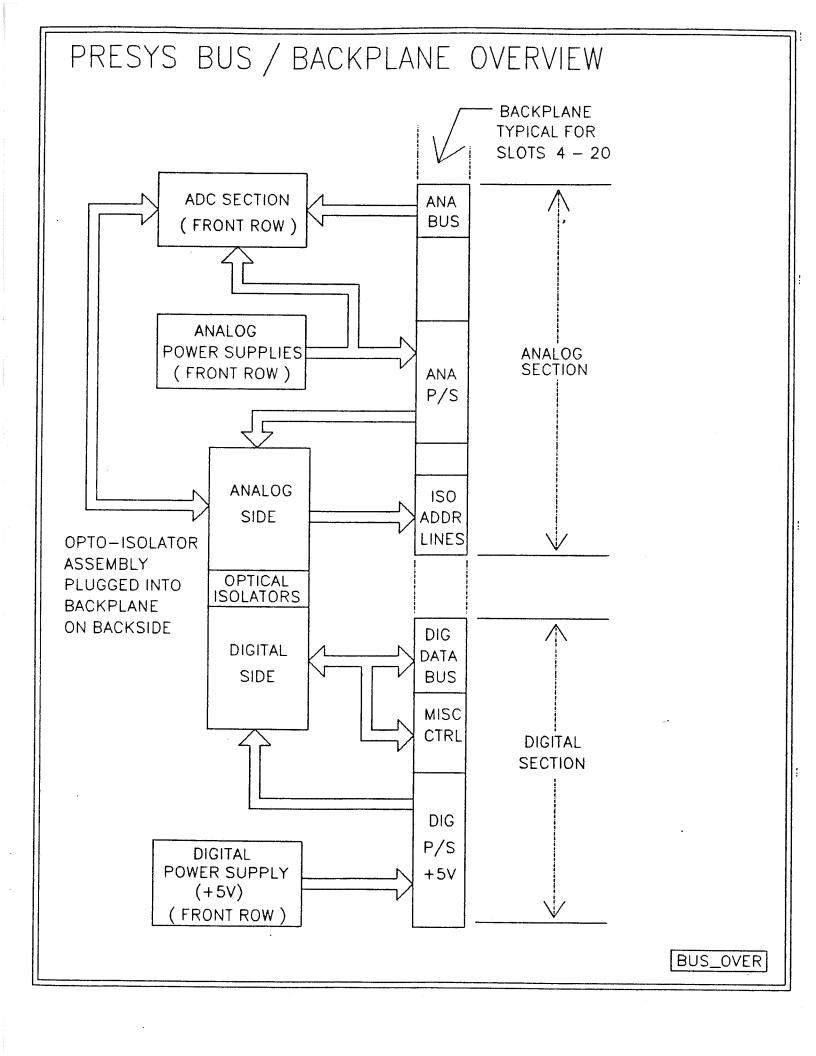

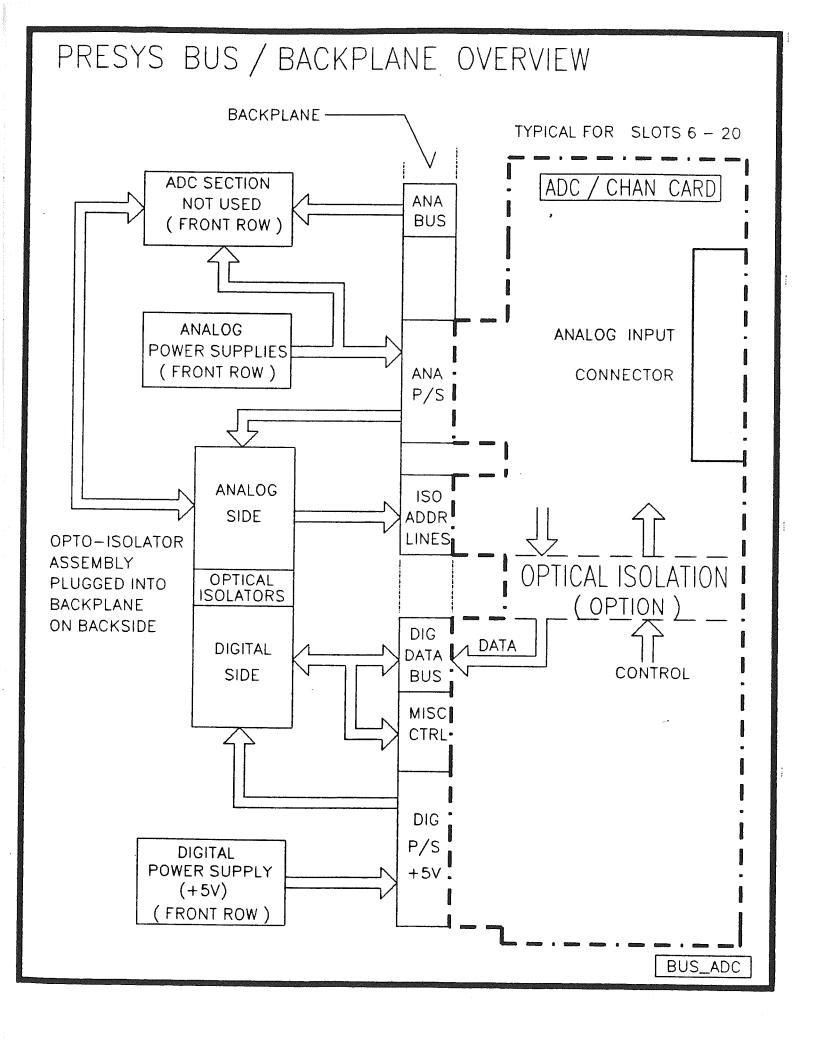

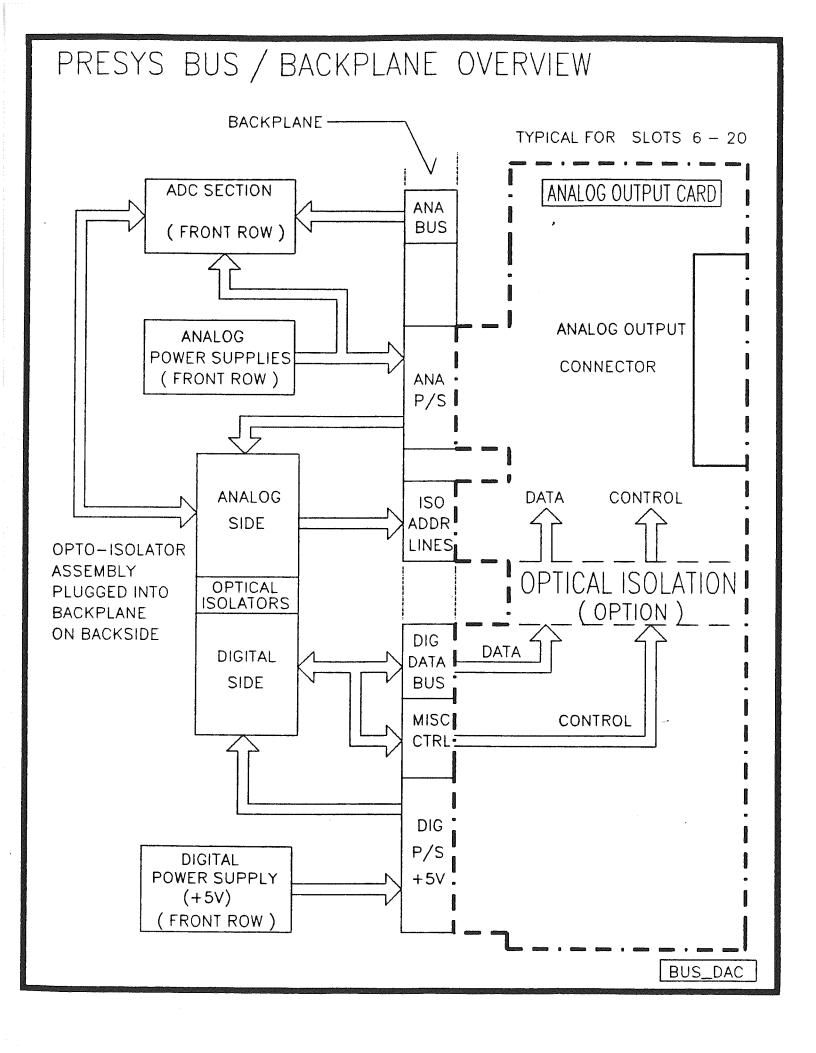

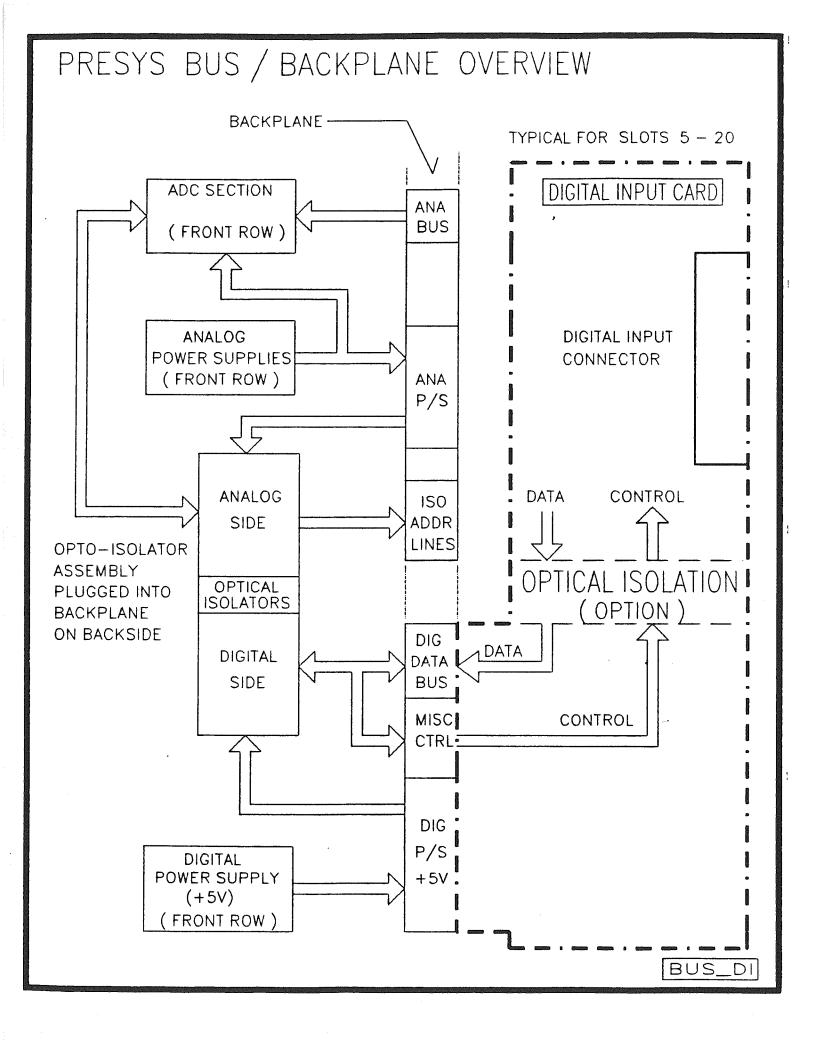

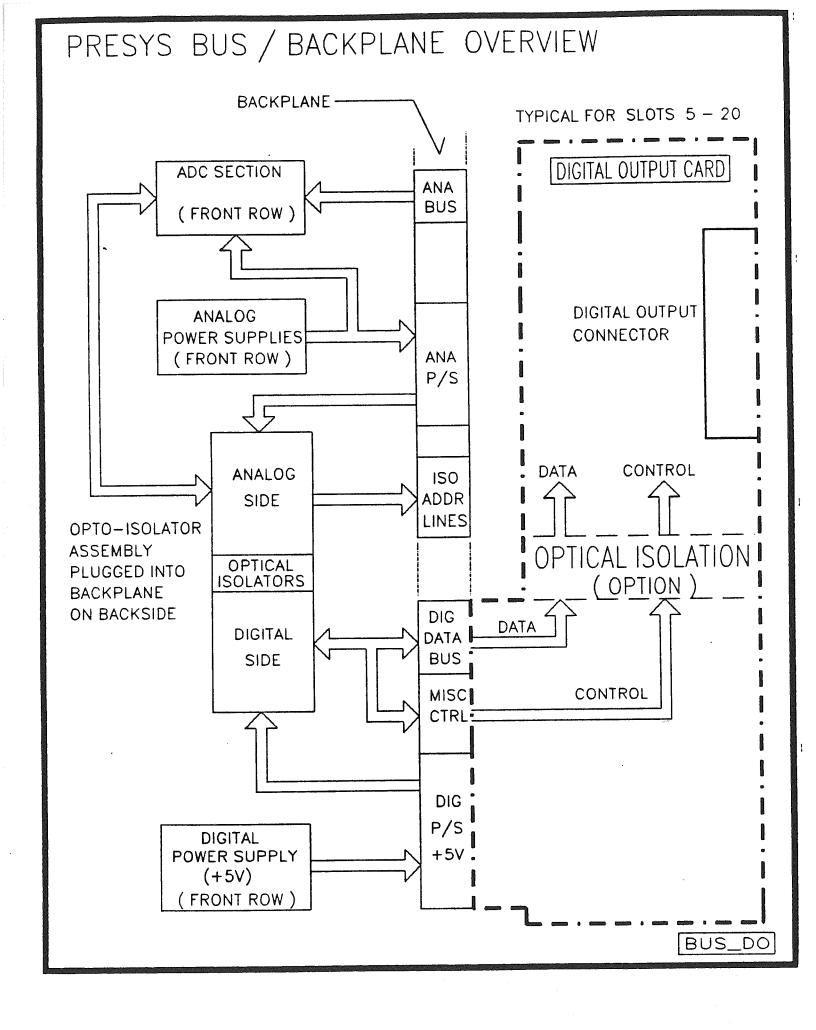

#### PRESYS BUS/BACKPLANE OVERVIEW

This document presents a generalized "OVERVIEW" of the backplane connections related to the various types of I/O cards used in both PRESYS 1000 and PRESYS 4000 systems. It does not discuss bus timing, define control signals, or list pin assignments.

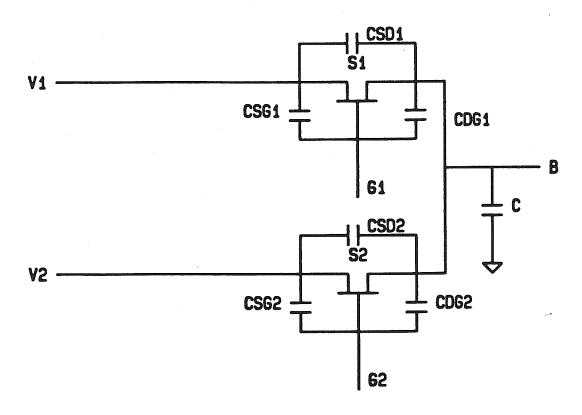

PRESYS 1000 systems use a single ADC preceded by an analog multiplexer. They are intended to scan multiple channels with relatively low conversion rates per channel. Depending upon the ADC installed they may be clocked for aggregate rates of up to 1MHz. Channel selection is programmable.

PRESYS 4000 systems use an ADC per channel cards with outputs digitally multiplexed into a single data stream. They are intended to scan multiple channels with relatively high conversion rates per channel. Since all channels are clocked simultaneously, time correlated data is generated.

The maximum clock rates depends upon the type and number of ADC per channel cards included in the system. All cards installed will be scanned in sequence determined by physical location. The maximum aggregate data rate is 5MHz.

#### NOTE:

If the maximum aggregate rate of the PRESYS 4000 system is below 1MHz, it may be factory configured as a PRESYS 1000 system which includes all of the channel selection options.

The backplane extends across all 20 slots of the back row of the PPESYS chassis. The description herein applies only to the slots available for user connections (5-20).

There are two basic sections of the backplane; ANALOG and DIGITAL. To minimize system noise, each section is connected to a separate power supply. Reference Figure BUS\_OVER. User I/O cards may be plugged into any of the referenced slots. The only make connections to the appropriate power supplies.

Most analog cards require control signals generated by digital cards located in slots 1-3. Since these signals are referenced to the digital power supply they are routed through an optical isolator assembly mounted on the rear side of the backplane.

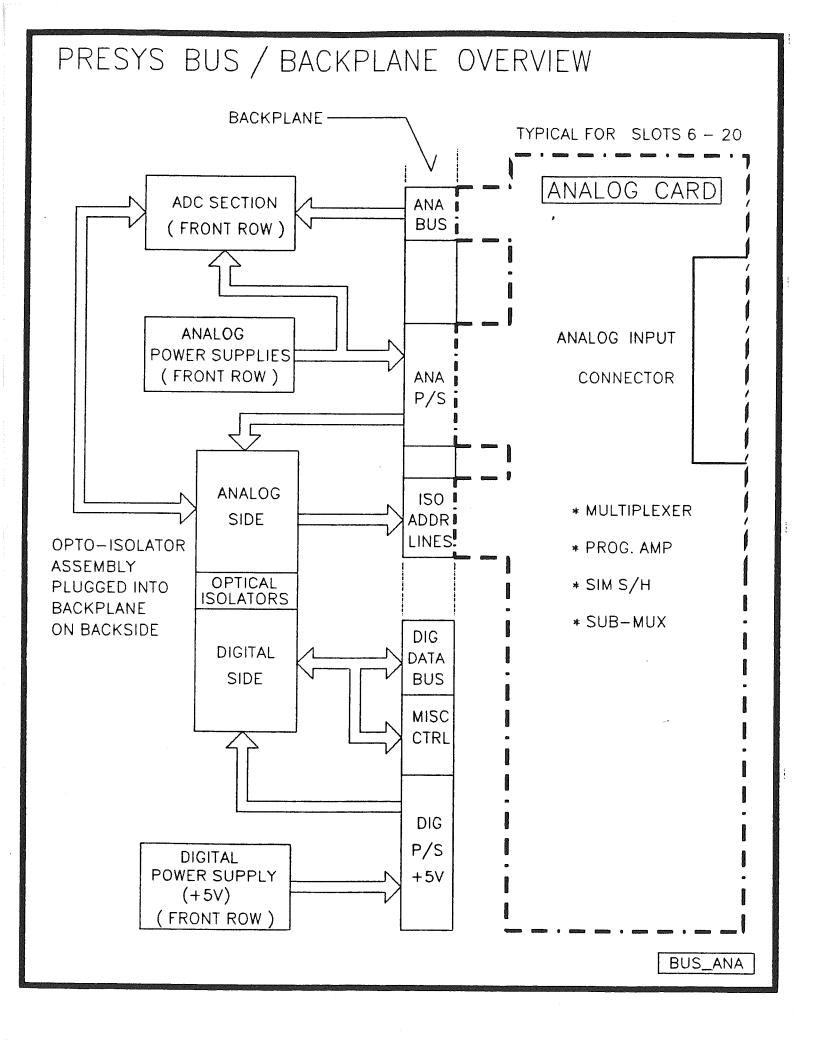

#### PRESYS BUS/BACKPLANE OVERVIEW

ANALOG cards include: (Reference Figure BUS\_ANA)

- \* 16 channel differential multiplexers

- \* 16 channel single-ended, buffered multiplexers

- \* 8 channel simultaneous sample-and-holds

- \* 2 channel programmable gain amplifiers

- \* 1 channel programmable gain, filter 'amplifiers

#### DIGITAL cards include: (Reference Figure BUS\_DIG)

- \* 1 channel, 16 line digital input

- \* 2 channel, 16 line digital input

- \* 1 channel, 16 line digital output

- \* 2 channel, 16 line digital output

- \* Assorted computer compatible interfaces (SCSI, IEEE-488, DR11-W, etc.)

#### Two other types of cards used in PRESYS systems are:

- \* Analog-to-Digital converter per channel: (Reference Figure BUS\_ADC)

- \* 1 channel, 16 bit Analog-to-Digital converter

- \* 2 channel, 16 bit Analog-to-Digital converter

- \* 4 channel, 12 bit Analog-to-Digital converter

- \* Digital-to-Analog converter (Reference Figure BUS\_DAC)

- \* 8 channel, 12 bit Digital-to-Analog converter

- \* 4 channel, 16 bit Digital-to-Analog converter

These two groups of cards connect to both the ANALOG and DIGITAL sections of the backplane. Unless they include onboard optical isolation, the ANALOG and DIGITAL power supplies will no longer be isolated. Since this is acceptable in many systems, optical isolation on these cards is available as an option, and not included as a standard feature.

The Analog-to-Digital converter per channel cards use the ANALOG power supplies on input sides. The outputs connect to the digital data bus which is referenced to DIGITAL ground. Optional optical isolators on these cards break this connection.

The Digital-to-Analog converter cards receive input data and control signals from the DIGITAL section of the backplane but require voltages from the ANALOG power supplies on outputs. Optional optical isolators on digital I/O lines break connections between the ANALOG and DIGITAL power supplies.

#### PRESYS BUS/BACKPLANE OVERVIEW

The ANALOG section is common to slots 4 through 20, but analog cards normally plug into slots 6 - 20. It basically consists of:

- \* Analog power supply

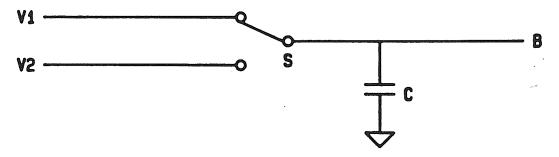

- \* Analog bus connected to multiplexer switch outputs on analog plug-in cards. This is also connected to the input of the Analog-to-Digital converter located in the front row of the PRESYS 1000 systems. It is not used on PRESYS 4000 systems.

- \* Isolated address and control lines needed by Analog cards

The DIGITAL section is common to the entire 20 slots, but user connections are limited to slots 5-20. It basically consists of:

- \* Digital power supply (+5 volts)

- \* 16 line digital data bus

- \* Miscellaneous control lines

#### Reference Figures:

FIGURE 3-9A BUS\_OVER BUS\_ANA BUS\_DIG BUS\_ADC BUS\_DAC

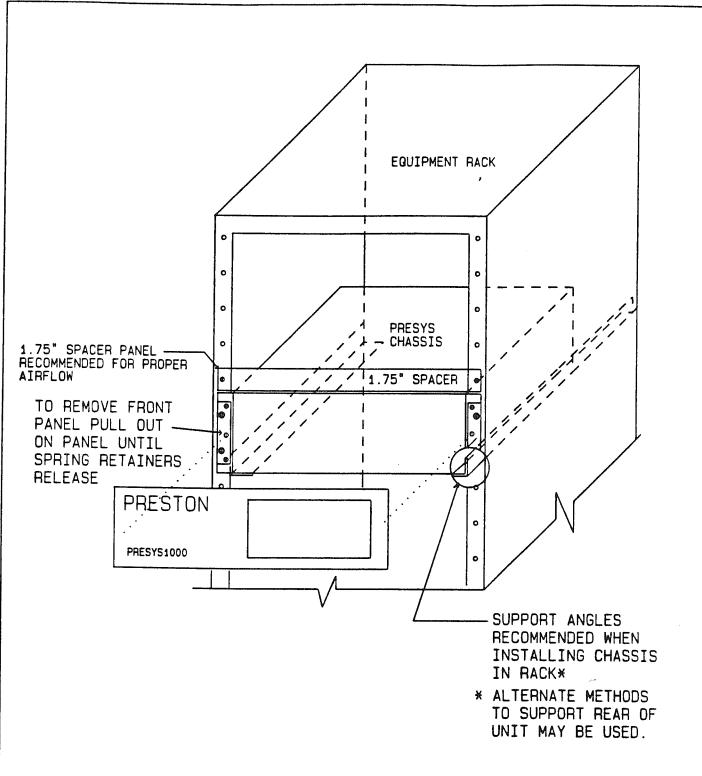

#### INSTALLATION

The figure on the following page indicates the preferred method for mounting a PRESYS system chassis into a cabinet. Rails, as indicated, or some alternate device are required to support the weight.

Since the PRESYS systems may be installed into many types of cabinets the rails are NOT supplied by Preston.

The top cover of the PRESYS chassis has slots for airflow. A spacer panel of at least 1.75 inches in height(minimal RETMA standard) should be installed directly above this unit. This assures that the airflow in the unit will be approximately the same when installed in a rack as on the bench where calibration was performed.

Blank panels are installed in all empty slots in the rear of the chassis to block airflow through these openings and keep all input air passing over the cards installed. If some new item should be added the corresponding blank cover must first be removed. If a card is removed, one should be installed. If not available, use some other temporary material to cover the resulting opening.

It would be good practice to save the blank panels if an item is removed. If some other module is removed for any reason this cover can be installed in its place. It is also a good idea to save the shipping container in case the unit should need be sent back to the factory or some other authorized service center.

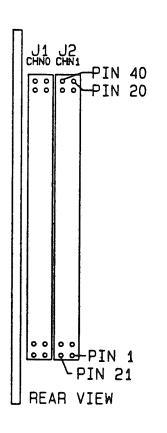

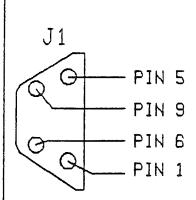

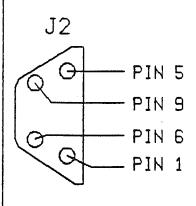

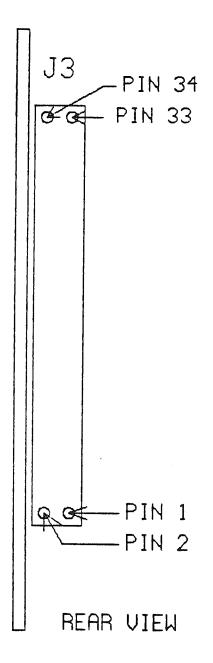

All user connections to the PRESYS are made via connectors mounted on the back of the plug in cards.

After the PRESYS 1000 chassis has been installed in the cabinet the following procedure is recommended:

- \* A: Verify power switch is in the OFF position. If not place it to the OFF position.

- B: Verify that input ac voltage in the cabinet agrees with that indicated on power tag mounted above power cord.

- \* C: With input signal sources set to nominal O volt levels make appropriate connections to input signals.

- D: Connect interface cables to computer or external controller.

- \* E: Place power switch to the ON position and allow a 1 hour warm up period to guarantee rated accuracy.

- \* F: During the warm up time the system is operational and may be used for all functions but at a lesser degree of accuracy from the analog components.

PRESYS 1000 INSTALLATION

PRESTON SCIENTIFIC

PRESYS 1000

FRONT PANEL QUICK REFERENCE

#### OPERATOR KEY DESCRIPTIONS

Must press this key for any DATA entry. Makes keys the hexidecimal value black screened on the keys. Sometimes this key is used to move to another display.

This key places all keys back to their FUNCTION mode, the white screened lettering on the key.

This key CLEARS an entry leaving that display unchanged or scrolls a display BACKWARD.

This key causes system to accept an ENTRY or scrolls a display FORWARD.

## KEY DEFINITIONS

| KEY       | DESCRIPTION FI                                                                                    | GURE       |

|-----------|---------------------------------------------------------------------------------------------------|------------|

| CNTL<br>0 | Display / change CONTROL WORD or EXTENSION WORD Display individual CONTROL BITS or EXTENSION BITS |            |

| SPCL<br>1 | Load User defined defaults                                                                        | 102        |

| B/L       | Change modes REMOTE / LOCAL                                                                       | 103        |

| STRT<br>3 | Display / change INTERNAL or EXTERNAL START mode . :                                              | 104        |

| CCLK<br>4 | Display / change BURST CHANNEL RATE CLOCK or PRESCALE CLOCK divisor                               | 105        |

| SCLK<br>5 | Display / change SCAN CLOCK divisor or CLOCK SOURCE                                               | 106        |

| BRST<br>6 | Display / change BURST or NON-BURST mode                                                          | 107        |

| SEQ<br>7  | Display / change SEQUENTIAL or RANDOM mode                                                        | 108        |

| CAM<br>B  | Display / change CAM ENABLED or CAM DISABLED mode Display / change CAM ADDRESS or CAM DATA        | 109<br>110 |

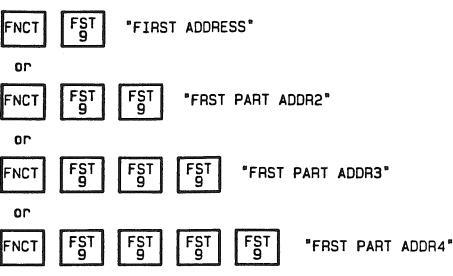

| FST<br>9  | Display / change FIRST CHANNEL ADDRESS or 2nd, 3rd, 4th PARTITION FIRST ADDRESSES                 | 111        |

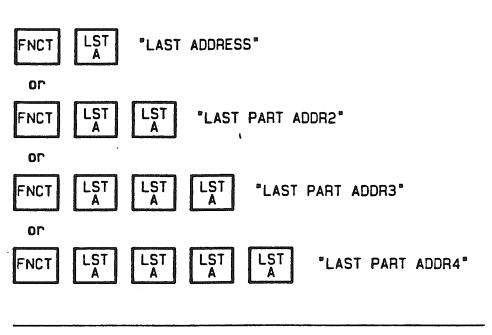

| LST       | Display / change LAST CHANNEL ADDRESS or                                                          | 112        |

## KEY DEFINITIONS

| KEY       | DESCRIPTION                                                                                                                                                                                                                                                                            | FIG                          | URE                      |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------|

| ENVR<br>B | Display / change ENVIROMENT information Display WAITING FOR information (env Display ERROR LIST (env Display PROM REV and DATE (env Display / change ADC DATA DISPLAY FORMAT . (env Display / change CAM DATA DISPLAY FORMAT . (env Display / change MISCELLANEOUS SETTINGS (env       | 2) .<br>3) .<br>4) .<br>5) . | 114<br>115<br>116<br>117 |

|           | ADC RESOLUTION ADC OFFSET ADC FULLSCALE REMAKE DEFAULTS CRYSTAL FREQUENCY EXTERNAL MUXCLK source with EXT BURST CLOCK STOP* CLOCK SOURCE MASTER OF SLAVE chassis EXTERNAL START EDGE EXTERNAL CLOCK EDGE STOP* OF COIN START SIMULTANEOUS HOLD CAM ENABLE CAM RESTART EDGE DIAGNOSTICS |                              |                          |

| RUN<br>C  | Place system into a LOCAL RUN condition Display ADC DATA or DIGITAL IN DATA                                                                                                                                                                                                            | • •                          | 121                      |

| STOP<br>D | Place system into a LOCAL STOPPED condition                                                                                                                                                                                                                                            |                              | 122                      |

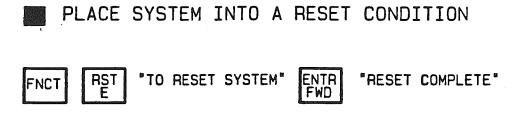

| RST<br>E  | Place system into a RESET condition                                                                                                                                                                                                                                                    | <br>set)                     | 123<br>124               |

| AUX<br>F  | Display / change BUS TALK DATA or ANALOG BUS DATA                                                                                                                                                                                                                                      |                              | 125                      |

#### DISPLAY CONTROL WORD or EXTENSION WORD

FNCT CNTL "CONTROL WORD"

OF

FNCT CNTL CNTL "EXTENSION WORD"

#### CHANGE CONTROL WORD or EXTENSION WORD

Use above steps to get the desired display, then press

$egin{array}{c|c} egin{array}{c|c} egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{ar$

ENTR FWD

use RACK to restore to original state

use FNCT to put panel in function mode

#### DISPLAY CONTROL WORD or EXTENSION WORD

FNCT CNTL "CONTROL WORD"

or

FNCT CNTL CNTL "EXTENSION WORD"

DISPLAY CONTROL BITS or EXTENSION BITS

Use above steps to get the desired display, then press

ENTR FWD to scroll Forward through the control bits , or

CLR to scroll Backward through the control bits.

use FNCT to put panel in function mode

### LOAD USER DEFINED DEFAULTS

FNCT SPCL ENTR DATA SPCL ENTR FWD

figure 102

CHANGE MODES REMOTE / LOCAL

FNCT R/L "REMOTE REGISTERS"

or

FNCT R/L "LOCAL REGISTERS"

use FNCT to put panel in function mode

## DISPLAY START MODE

"INT START" "EXT START"

CHANGE START MODE

STRT 3

"INT START"

OF

"EXT START"

use FNCT to put panel in function mode

# DISPLAY BURST CHANNEL RATE CLOCK or PRESCALE DIVISOR

FNCT CCLK "BURST CHAN CLK"

OF

FNCT CCLK CCLK "CLOCK PRESCALE"

# CHANGE BURST CHANNEL RATE CLOCK or PRESCALE DIVISOR

Use above steps to get the desired display, then press

DATA followed by the Divisor value desired . then press

ENTR FWD

use BACK to restore to original state

use FNCT to put panel in function mode

# DISPLAY SCAN CLOCK DIVISOR or CLOCK SOURCE

FNCT

SCLK 5

"SCAN RATE CLK"

or

FNCT

SCLK 5

"SCAN RATE CLK"

ENTR FWD "INTERNAL SOURCE"

or

"EXTERNAL SOURCE"

# CHANGE SCAN CLOCK DIVISOR or CLOCK SOURCE

To change the Divisor press .

FNCT

SCLK 5

then press

DATA

followed by the Divisor value desired . then press

ENTR FWD

To change clock source press .

FNCT

SCLK 5 ENTR FWD "INTERNAL SOURCE"

or

"EXTERNAL SOURCE"

ENTR' FWD

use BACK to restore to original state

use FNCT to put panel in function mode

### DISPLAY BURST MODE

FNCT

BRST 6 "BURST MODE"

or

"NON-BURST MODE"

CHANGE BURST MODE

FNCT

BRST 6 "BURST MODE"

or

"NON-BURST MODE"

ENTR FWD

use FNCT to put panel in function mode

#### DISPLAY SEQUENCE MODE

FNCT

SEQ 7

- "RANDOM MODE"

- "SEQUENCE MODE"

CHANGE SEQUENCE MODE

FNCT

SEQ 7 "RANDOM MODE"

"SEQUENCE MODE"

ENTR FWD

use FNCT to put panel in function mode

# DISPLAY CAM MODE

FNCT

CAM 8 "ENABLE CAM" Or "DISABLE CAM"

CHANGE CAM MODE

FNCT

CAM 8 "ENABLE CAM"

OF

"DISABLE CAM"

ENTR FWD

use FNCT to put panel in function mode

### DISPLAY CAM DATA

"CAM ADDR = " "CAM DATA

ENTR FWD

to scroll Forward through CAM list . or

CLR BACK

to scroll Backward through CAM list.

#### CHANGE CAM DATA

■ METHOD 1: CHANGE OF DATA BETWEEN FIRST AND LAST Use above steps to advance to desired location, press

DATA

DATA

followed by the desired data value, then press

METHOD 2: . CHANGE OF DATA AT ANY LOCATION Use above steps to get to CAM display, then press

DATA

followed by the desired address value, then press

FWD

Next press

DATA

followed by the data value desired,

then press

ENTR FWD

to restore to original state

to put panel in function mode

# CHANGE FIRST CHANNEL ADDRESS or FIRST PARTITION ADDRESSES

Use above steps to get the desired display, then press

DATA followed by the Address value desired . then press

ENTR FWD

use CLR to restore to original state

use FNCT to put panel in function mode

# DISPLAY LAST CHANNEL ADDRESS or LAST PARTITION ADDRESSES

# CHANGE LAST CHANNEL ADDRESS or LAST PARTITION ADDRESSES

Use above steps to get the desired display, then press

DATA followed by the Address value desired. then press

ENTR F₩D

use BACK to restore to original state

use FNCT to put panel in function mode

# DISPLAY WAITING FOR INFORMATION.

FNCT ENVR "ENVIROMENT = 1" ENTR "WAITING FOR"

figure 113

## DISPLAY ERROR LIST

FNCT ENVR DATA R/L ENTR "ERR 1 = "

ENTR to scroll Forward through the list

CLR to scroll Backward through the list

figure 114

# DISPLAY PROM REVISION AND DATE

FNCT ENVR DATA STRT ENTR PROM1 9988-XX

ENTR "PROM2 9989-XX"

use FNCT to put panel in function mode

# DISPLAY ADC DATA FORMAT FOR DISPLAY ENTR "SIGNAL = " FNCT CHANGE ADC DATA FORMAT FOR DISPLAY Use above steps to get to the format display, then press followed by the value corresponding to the desired DATA display format. Then press figure 116 DISPLAY CAM DATA FORMAT FOR DISPLAY and DATA ENTRY "CAM DATA = " FNCT CHANGE\_CAM DATA FORMAT FOR DISPLAY Use above steps to get to the format display, then press followed by the value corresponding to the desired DATA display format. Then press

# DISPLAY MISCELLANEOUS ENVIROMENT SETTINGS

FNCT ENVR DATA BRST ENTR "ADC RESOLUTION"

ENTR to scroll Forward through the list settings, or

CLR BACK to scroll Backward through the list settings.

# CHANGE MISCELLANEOUS ENVIROMENT SETTINGS

Use above steps to get to the desired setting, then press

DATA followed by the value corresponding to the desired setting, then press ENTR FWD

use BACK to restore to original state

use FNCT to put panel in function mode

## DISPLAY BOARD DEFINITION TABLE

FNCT ENVR DATA SEG ENTR "BD 0 TYPE 8000"

ENTR to scroll Forward through the list settings, or

CLR to scroll Backward through the list settings.

## CHANGE BOARD DEFINITION TABLE

DATA followed by the value corresponding to the desired setting, then press ENTR . If the data for the setting is already as desired then press EACK to skip to the next setting for that board.

use CLR BACK to restore to original state

use FNCT to put panel in function mode

## DISPLAY REMOVED BOARD LIST

FNCT ENVR DATA CAM ENTR "REMOVED BOARD O"

ENTR to scroll Forward through the list, or

CLA to scroll Backward through the list.

### CHANGE REMOVED BOARD LIST

use FNCT to put panel in function mode

# PLACE SYSTEM INTO LOCAL RUN CONDITION OF DISPLAY ADC DATA OF DIGITAL IN DATA

FNCT

RUN C

"CHANNEL = 0"

ENTR FWD

to scroll Forward through the active channels, or

CLR BACK

to scroll Backward through the active channels

# CHANGE CHANNEL DISPLAYED

Use above steps to get to the channel display, then press

DATA

followed by the address of the channel to display.

then press

. Data will only be displayed on those

channels scanned.

use FNCT to put panel in function mode

# PLACE SYSTEM INTO A LOCAL STOP CONDITION FNCT STOP "SYSTEM STOPPED" figure 122

figure 123

PUT SYSTEM INTO FACTORY DEFAULT STATE

Hold the RST while powering up the system.

use FNCT to put panel in function mode figure 124

# DISPLAY BUS TALK DATA

FNCT AUX "ID ADDRS = "

BUS DATA = "

ENTR FWD to send data as shown on display to the Bus.

If ID = 100, the data will also be sent to the Analog

Data Bus.

# CHANGE ID or BUS DATA

- To change the ID address, use steps above to get to the ID BUS display, then press DATA followed by ID data, then press ENTR FWD

- To change the BUS data, use the steps above to get to the ID BUS display, then press DATA DATA followed by BUS data, then press ENTR FWD

use CLR to restore to original state

use FNCT to put panel in function mode

figure 125

PRESYS 1000

FRONT PANEL CONTROLS

#### CONTROL PANEL KEY STROKES

The sequence of keystrokes is based on the assumption that the user is always starting from the "FUNCTION" level (first level) which can be reached by pressing the key labeled "FNCT". In general, except when the system is waiting for data to be entered, the system will remain at the "FUNCTION" level.

When a display is followed by an "L" or an "R", this will remind the user that the information displayed is from the "Local" or from the "Remote" registers. Only formatting and display parameters may be entered in the "REMOTE" mode while all parameters may be entered in the "LOCAL" mode. If the computer has set the "LOCAL LOCKOUT" bit in the 'CONTROL WORD" then the "LOCAL" mode will be restricted to the same entries as the "REMOTE" mode.

The keys are designated as follows:

| <u>KEY</u> | <b>FUNCTION</b> | DESCRIPTION                            |

|------------|-----------------|----------------------------------------|

| 0          | CNTL            | Command Control Word                   |

| í          | SPCL            |                                        |

|            |                 | Special Control Functions              |

| 2          | R/L             | Remote Local Register Mode Control     |

| 3          | STRT            | Start Mode and Start Control           |

| 4          | CCLK            | Clock Prescaler and Burst Channel Rate |

| 5          | SCLK            | Scan Rate Clock                        |

| 6          | BRST            | Burst or Non-Burst Mode                |

| 7          | SEQ             | Sequence or Random Mode                |

| 8          | CAM             | Cam Enable/Disable and Data            |

| 9          | FST             | First Channel Data                     |

| A          | LST             | Last Channel Data                      |

| B          | ENVR            | Set System Environment                 |

| C          | RUN             | Start System and Read Channel Data     |

| D          | STOP            | Stop the System                        |

| E          | RST             | Reset the System                       |

| F          | AUX             | Auxiliary Functions                    |

| CB         | CLR BACK        | Clear Entry or Backspace               |

| DA         |                 | Enable Data Display and Entry          |

| EF         |                 |                                        |

|            |                 |                                        |

| FN         | FNCT            | Return to the FUNCTION Level           |

The functional description of each control panel key is described in the following paragraphs. A hexadecimal coding is used to number the paragraphs so that the number of the each paragraph represents the sequence of keystrokes necessary to reach the described function. In addition to the sixteen data keys are the four control keys, "DATA", "FNCT", "CLR BACK", and "ENTR FWD". These four keys are abbreviated to "DA", "FN", "CB", and "EF". A double dot (..) following a key indicates one or more repeat pressings of that key.

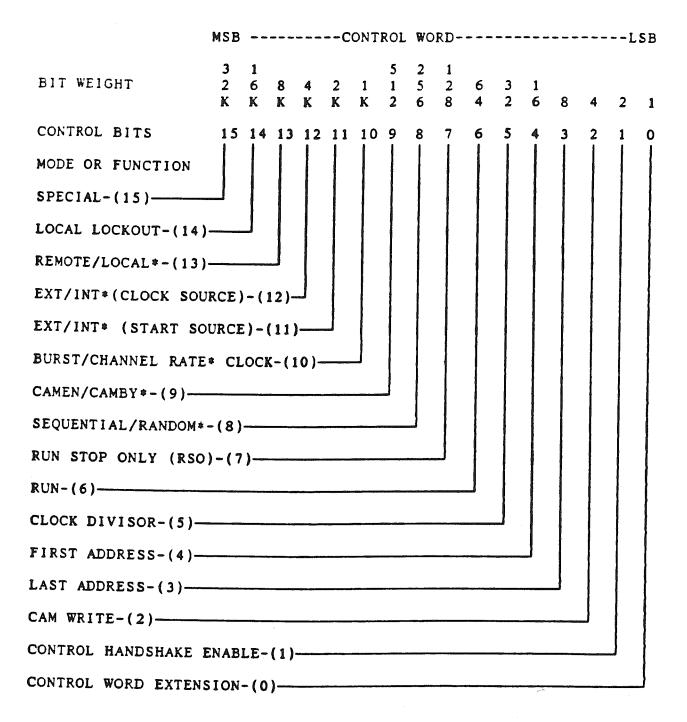

#### O The "CNTL" key.

The "CNTL" key performs three functions, view the Command Word, change the Command Word, and view the decoded bits of the Command Word.

Pressing the "CNTL" (0) key will cause the first line of the display to read "CONTROL WORD" followed by an "L" or an "R". On the second line of the display is the 16 bit Command Word displayed in binary notation.

O.DA The Control Word data entry mode in "LOCAL" only.

In this mode a flashing cursor appears over one of the binary bits of the displayed Control Word. The data bit can be changed or the cursor moved.

- O.DA.O Cause the data bit at the cursor to be a zero and the cursor to move to the right to the next bit that the user is permitted to change.

- O.DA.1 Cause the data bit at the cursor to be a one and the cursor to move to the right to the next bit that the user is permitted to change.

- O.DA.n.CB Where "n" is a "0" or a "1", pressing the "CLR BACK" key will cause the cursor to move to the left to the next previous bit that the user is permitted to change.

- O.DA.n.EF Where "n" is any number of "0", "1", or "CLR BACK" key pressings, pressing the "ENTR FWD" key will cause the modified Control Word to be entered.

- O.CB Cause the first line of the display to read "BIT NUMBER 1" followed by "L" or "R". The second line of the display will display the decoded control function together with it's state.

- O.CB.. Subsequent pressing of the "CLR BACK" key will cause the bit number to increment through the bits of the control word displaying the state and function of each bit.

- O.EF Cause the first line of the display to read "BIT NUMBER 15" followed by "L" or "R". The second line of the display will display the decoded control function together with it's state.

- O.EF.. Subsequent pressing of the "ENTR FWD" key will cause the bit number to decrement through the bits of the control word displaying the state and function of each bit.

- O.n.. Where "n" is any number of "ENTR FWD" and "CLR BACK" key pressings will increment and decrement through the bits of the control word displaying the state and function of each bit.

#### 1 The "SPCL" key.

The "SPCL" key reloads the default system parameters in "LOCAL" only.

Pressing the "SPCL" (1) key will cause the first line of the display to read "SPECIAL FUNCTION". The second line of the display will read "PRESS ENTR/FWD".

- 1.EF Pressing the "ENTR FWD" key will cause the first line of the display to read "DEFLT PARAMTRS". The second line of the display will read "O=NO 1=YES.

- 1.EF.DA Pressing the "DATA" key will cause the blinking cursor to appear at the end of the second line in "LOCAL" only.

- 1.EF.DA.0 Pressing the "0" key will display a "0" at the blinking cursor.

- 1.EF.DA.O.EF Pressing the "ENTR FWD" key will cause the control word to be displayed as in step 0 without change.

- 1.EF.DA.1 Pressing the "1" key will display a "1" at the blinking cursor.

- 1.EF.DA.1.EF Pressing the "ENTR FWD" key will cause the control word to be changed to the default value and displayed as in step 0.

#### 2 The "R/L" key.

Pressing the "R/L" (2) key will cause the mode of the other keys to change between displaying (only) the data stored in the remote registers and displaying and changing, if desired, the data stored in the local registers. Each time this key is pressed the mode will change. The first line of the display will read "LOCAL REGISTERS" or "REMOTE REGISTERS" as applicable.

#### 3 The "STRT" key.

The "STRT" key will display and change the start mode of the system between internal and external start.

Pressing the "STRT" (3) key will cause the first line of the display to read "INT START" or "EXT START", depending on the current mode of the system, followed by an "L" or an "R". If the display is in the remote mode and an, "R" is displayed, the second line of the display will remain blank. If the display is in the local mode and an "L" is displayed then the second line will read "PRESS ENTR/FWD".

3.EF Pressing the "ENTR FWD" key when in the local display mode will cause the system to switch to the alternate mode which will be displayed.

#### 4 The "CCLK" key.

The "CCLK" key will display and change the Burst Mode Channel Rate Clock and the Master Clock Prescaler. Pressing this key repetitively will cause the display to toggle between the Burst Mode Channel Rate Clock and the Master Clock Prescaler.

Pressing the "CCLK" (4) key will cause the first line of the display to read "BURST CHAN CLK", followed by an "L" or an "R". The second line of the display will read "DIV = nnn", where "nnn" is the decimal value of the divisor that divides the System Operating Clock down to the Burst Channel Clock rate.

- 4.DA Pressing the "DATA" key while in the "LOCAL" mode will cause the second line of the display to read "DIV =" only with a flashing cursor at the position of the first digit of the divisor value.

- 4.DA.n.. Pressing the keys "0" through "9" will record a new value for the Burst Channel Clock Divisor.

- 4.DA.n..CB Pressing the "CLR BACK" key will delete the new entry, retaining the old divisor value, and change the display to be the same as prior to pressing the "DATA" key.(PRS4).

- 4.DA.n..EF Pressing the "ENTR FWD" key will cause the new divisor to be entered into the system.

- 4.4 Pressing the "CCLK" key a second time will cause the first line of the display to read "CLOCK PRESCALE", followed by an "L" or an "R". The second line of the display will read "DIV = nnn", where "nnn" is the decimal value of the divisor that divides the System Operating Clock down to the Prescaler Clock rate.

- 4.4.DA Pressing the "DATA" key while in the "LOCAL" mode will cause the second line of the display to read "DIV =" only with a flashing cursor at the position of the first digit of the divisor value.

- 4.4.DA.n.. Pressing the keys "0" through "9" will record a new value for the Prescaler Clock Divisor.

- 4.4.DA.n..CB Pressing the "CLR BACK" key will delete the new entry, retaining the old divisor value, and change the display to be the same as if the 4.4 key stroke had been pressed.

- 4.4.DA.n..EF Pressing the "ENTR FWD" key will cause the new divisor to be entered into the system, and change the display to be the same as if the 4.4 key stroke had been pressed.

#### 5 The "SCLK" key.

The "SCLK" key will display and change the Scan Rate Clock which is the clock that sets the rate at which the Burst Scans occur in the Burst Mode and the rate at which the channels are scanned in the non-burst mode.

Pressing the "SCLK" (5) key will cause the first line of the display to read "SCAN RATE CLK", followed by an "L" or an "R". The second line of the display will read "DIV = nnn", where "nnn" is the decimal value of the divisor that divides the System Operating Clock down to the Scan Rate Clock.

- 5.DA Pressing the "DATA" key in the "LOCAL" mode will cause the second line of the display to read "DIV =" only with a flashing cursor at the position of the first digit of the divisor value.

- 5.DA.n.. Pressing the keys "0" through "9" will record a new value for the Scan Rate Clock Divisor.

- 5.DA.n..CB Pressing the "CLR BACK" key will delete the new entry, retaining the old divisor value, and change the display to be the same as if a "5" key stroke had been pressed.

- 5.DA.n..EF Pressing the "ENTR FWD" key will cause the new divisor to be entered into the system.

- 5.EF Pressing the "ENTR FWD" key in the "LOCAL" mode will cause the source of the scan clock to switch between internal and external.

#### 6 The "BRST" key.

The "BRST" key will display and change the running mode of the system between burst mode and non-burst mode.

Pressing the "BRST" (6) key will cause the first line of the display to read "BURST MODE" or "NON-BURST MODE", depending on the current mode of the system, followed by an "L" or an "R". If the display is in the remote mode and an "R" is displayed, the second line of the display will remain blank. If the display is in the local mode and an "L" is displayed then the second line will read "PRESS ENTR/FWD".

6.EF Pressing the "ENTR FWD" key when in the local display mode will cause the system to switch to the alternate mode.

#### 7 The "SEQ" key.

The "SEQ" key will display and change the running mode of the system between the sequence mode and the random mode.

Pressing the "SEQ" (7) key will cause the first line of the display to read "SEQUENCE MODE" or "RANDOM MODE", depending on the current mode of the system, followed by an "L" or an "R". If the display is in the remote mode and an "R" is displayed, the second line of the display will remain blank. If the display is in the local mode and an "L" is displayed then the second line will read "PRESS ENTR/FWD".

7.EF Pressing the "ENTR FWD" key when in the local display mode will cause the system to switch to the alternate mode.

#### 8 The "CAM" key.

The "CAM" key will display and change the enabled or disabled status of the channel address memory and display and enter data into the memory.

Pressing the "CAM" (8) key will cause the first line of the display to read "ENABLE CAM" or "DISABLE CAM", depending on the current mode of the system, followed by an "L" or an "R". If the display is in the remote mode and an "R" is displayed, the second line of the display will remain blank. If the display is in the local mode and an "L" is displayed then the second line will read "PRESS ENTR/FWD".

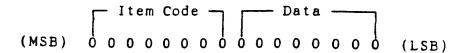

- 8.DA Pressing the "DATA" key will cause the first line of the display to read "CAM ADDR= nnnn", where "nnnn" is the First Address, and the second line of the display to read "CAM DATA= dddd", where "dddd" is the data stored in the addressed memory location. The address "nnnn" is always displayed in decimal notation and the data "dddd" is displayed in the format selected in the Environment entry function.

- 8.DA.DA Pressing the "DATA" key a second time will cause the first line of the display to read "CAM ADDR=", with the cursor placed at the position to enter a new address.

- 8.DA.DA.DA Pressing the "DATA" key a third time in the "LOCAL" mode will cause the first line of the display to read "CAM ADDR= nnnn", where "nnnn" is the current address, and the second line of the display to read "CAM DATA=" with the cursor placed at the position to enter the new cam data. The data must be entered in the same format as the data is displayed.

- 8.DA.DA.DA.n.. Pressing the keys "0" through "7", "0" through "9", or "0" through "F", will record a new value for the cam data.

- 8.DA.DA.DA.n..CB Pressing the key "CLR BACK" will delete the new value, retaining the old value, and change the display to be the same as if 8.DA.DA.n..EF key strokes had been pressed.

- 8.DA.DA.DA.n..EF Pressing the key "ENTR FWD" will cause the data to change to the entered value, and change the display to be the same as if 8.DA.DA.n..EF key strokes had been pressed.

- 8.DA.DA.n.. Pressing the keys "0" through "9" will record a new value for the address to be displayed.

- 8.DA.DA.n..CB Pressing the key "CLR BACK" will delete the new value, retaining the old value, and change the display to be the same as if 8.DA.DA key strokes had been pressed.

- 8.DA.DA.n..EF Pressing the key "ENTR FWD" will cause the address to change to the entered value, and change the display to be the same as if 8.DA.DA key strokes had been pressed.

- Pressing the "ENTR FWD" key will cause the cam address to advance to the next address and display that data.

- 8.DA.EF.. Pressing the "ENTR FWD" key additional times will cause the address to advance each time and display that data. When the Last Address has been reached the address will wrap around to the First Address.

- 8.DA.EF..DA Pressing the "DATA" key after any number of "ENTR FWD" keys is the same as key strokes 8.DA.DA for the displayed address (PRS4).

- 8.EF Pressing the "ENTR FWD" key when in the local display mode will cause the system to switch to the alternate mode.

#### 9 The "FST" key.

The "FST" key will display and change the First Channel which is the first sequencer position of any multiplexer scan.

Pressing the "FST" (9) key will cause the first line of the display to read "FIRST CHANNEL", followed by an "L" or an "R". The second line of the display will read "CHAN = nnn", where "nnn" is the decimal value of the current first channel.

- 9.DA Pressing the "DATA" key in the "LOCAL" mode will cause the second line of the display to read "CHAN =" only with a flashing cursor at the position of the first digit of the address value.

- 9.DA.n.. Pressing the keys "0" through "9" will record a new value for the First Channel.

- 9.DA.n..CB Pressing the "CLR BACK" key will backspace, deleting the most recently entered digit.

- 9.DA.n..EF Pressing the "ENTR FWD" key will cause the new first channel value to be entered into the system.

#### A The "LST" key.

The "LST" key will display and change the Last Channel which is the last sequencer position of any multiplexer scan.

Pressing the "LST" (A) key will cause the first line of the display to read "LAST CHANNEL", followed by an "L" or an "R". The second line of the display will read "CHAN = nnn", where "nnn" is the decimal value of the current last channel.

<u>A.DA</u> Pressing the "DATA" key in the "LOCAL" mode will cause the second line of the display to read "CHAN =" only with a flashing cursor at the position of the first digit of the address value.

- A.DA.n.. Pressing the keys "0" through "9" will record a new value for the Last Channel.

- <u>A.DA.n..CB</u> Pressing the "CLR BACK" key will backspace, deleting the most recently entered digit.

- A.DA.n..EF Pressing the "ENTR FWD" key will cause the new Last channel value to be entered into the system.

#### B The "PNVR" key.

The "ENVR" (B) key will display and change the Environment variables of the system. The environment variables include System Status, Error Status, date and version of the operating system, ADC data display format, CAM data display format, system default settings, the resolution of the ADC, the full scale and offset of the ADC in millivolts, and chassis setup information.

Pressing the "ENVR" key will cause the first line of the display to read "ENVIRONMENT = 1" and the second line of the display to read "PRESS ENTR/FWD".

<u>B.DA</u> Pressing the "DATA" key will cause the digit "1" to be replaced by the cursor.

<u>B.DA.n</u> Pressing keys "2" through "8" will select the desired ENVIRONMENT to view or change.

| ENV # | ENVIRONMENT                           |

|-------|---------------------------------------|

| 1     | EXPECTED COMMAND                      |

| 2     | ERROR HISTORY                         |

| 3     | PROM PART NUMBER, VERSION, AND DATE   |

| 4     | ADC DATA FORMAT                       |

| 5     | CAM DATA FORMAT                       |

| 6     | ADC RESOLUTION, OFFSET, FULL SCALE,   |

|       | REMAKE RESET, SET CRYSTAL FREQUENCY,  |

|       | EXTERNAL CLOCKS, STOP CLOCK SOURCE,   |

|       | MASTER/SLAVE, START PULSE EDGE, CLOCK |

|       | PULSE EDGE, START, SIM CAM BIT, CAM   |

|       | RESTART EDGE, DIAGNOSTIC CAM MODE.    |

| 7     | CHASSIS CIRCUIT BOARD LIST            |

| 8     | REMOVED BOARD LIST                    |

| U     | VEWOAED BOWKD F121                    |

B.DA.1.EF Pressing the B.DA.1.EF key sequence provides the user with the present state of the system in terms of the sequence of commands. If the system is running, the first line of the display will read "SYSTEM RUNNING". If the system is not running then the first line of the display will read "WAITING FOR" and the second line of the display will usually read "CONTROL WORD". In the event that an incomplete sequence of commands has been sent from the host

- computer then the second line of the readout may read "CAM DATA", "CLOCK DIV", "FST CHAN", "LST CHAN", "RUN ENABLE", or "START".

- B.DA.2.EF Pressing the B.DA.2.EF key sequence provides the user with a readout of up to 32 error codes. After 32 error codes have been recorded, any further errors will be disregarded until the 32 recorded error codes have been erased. Errors due to incorrect keyboard entries are not recorded.

- If there are no errors recorded then the first line of the display will read "NO ERRORS".

- If there are errors then the first line of the display will read "ERROR 1 = nn" where "nn" is the error code.

- B.DA.2.EF.. Additional pressing of the "ENTR FWD" key will cause the display to read the subsequent errors up to error number 32. After the last recorded error has been displayed, the first line of the display will read "TO CLEAR ERRORS", an the second line of the display will read "PRESS ENTR/FWD". if the "ENTR FWD" key is then pressed the recorded errors will be cleared from memory and the display will read "ERRORS CLEARED". Prior to erasing the errors, they should be recorded for diagnostic purposes.

- B.DA.2.EF..CB Pressing the "CLR BACK" key will cause the display to read the previous error.

- B.DA.3.EF Pressing the B.DA.3.EF key sequence provides the user with information about the operating system software. The first information is about the first PROM. The first line of the display will read "PROM1 nnnn-nn" where "nnnn-nn" is the part number of the PROM. The second line of the display will read "REV nn DATE mmyy" where "nn" is the revision number of the software on the PROM and "mmyy" is the month and year that the PROM was produced.

- B.DA.3.EF.EF Pressing the "ENTR FWD" key a second time will give information about the second PROM. The first line of the display will read "PROM2 nnnn-nn" where "nnnn-nn" is the part number of the PROM. The second line of the display will read "REV nn DATE mmyy" where "nn" is the revision number of the software on the PROM and "mmyy" is the month and year that the PROM was produced.

- <u>B.DA.3.EF.EF.EF</u> Pressing the "ENTR FWD" key a third time will toggle back to give information about the first PROM.

- B.DA.4.EF Pressing the B.DA.4.EF key sequence will display the format for displaying the ADC data. The first line of the display will read "SIGNAL = fffff" where "fffff" is "HEX, "OCTAL", "DEC", or "VOLTS".

- B.DA.4.EF.DA Pressing the "DATA" key will cause the second display line to read "O=O H=1 D=2 V=3" followed by a cursor.

- <u>B.DA.4.EF.DA.n</u> Pressing a key from "0" to "3" will select one of the formats.

- B.DA.4.EF.DA.n.CB Pressing the "CLR BACK" key will cancel the entry without changing the format.

- B.DA.4.EF.DA.n.EF Pressing the "ENTR FWD" key will enter the new format into the system.

- B.DA.5.EF Pressing the B.DA.5.EF key sequence will display the format for displaying the CAM data. The first line of the display will read "CAM DATA = fffff" where "fffff" is "HEX, "OCTAL", or "DEC".

- B.DA.5.EF.DA Pressing the "DATA" key will cause the second display line to read "O=O H=1 D=2" followed by a cursor.

- <u>B.DA.5.EF.DA.n</u> Pressing a key from "0" to "2" will select one of the formats.

- B.DA.5.EF.DA.n.CB Pressing the "CLR BACK" key

will cancel the entry without changing the

format.

- B.DA.5.EF.DA.n.EF Pressing the "ENTR FWD" key will enter the new format into the system.

- B.DA.6.(n)EF Pressing the B.DA.6 key sequence followed by (n) pressings of the "ENTR FWD" key will cause the following displays to appear:

- (n) DISPLAY DATA

1 "ADC RESOLUTION" NUMBER OF ADC BITS

"BITS =nn"

- 2 "ADC OFFSET" OFFSET FROM ZERO OF THE " MV =nnnnn" MIDPOINT OF THE RANGE

| 3  | "ADC FULL SCALE" " MV =nnnnn"  | ONE HALF OF THE ADC<br>RANGE                                                                                               |

|----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 4  | "UPDATE DEFAULTS" "O=NO 1=YES" | "YES" WILL LOAD CURRENT PARAMETERS INTO DEFAULTS                                                                           |

| 5  | "CRYSTAL FREQ" "DATA =nn"      | DESIRED CRYSTAL FREQUENCY<br>1, 4, 5, OR 10 MEGAHERTZ                                                                      |

| 6  | "EXT MUX-BRST CLK" "DATA=0"    | "1" OR "YES" WILL USE THE EXTERNAL CLOCK                                                                                   |

| 7  | "STOP CLOCK SRC" "DATA=0"      | "1" OR "YES" WILL USE<br>STOP* AS A CLOCK SOURCE                                                                           |

| 8  | "MASTER OR SLAVE" "DATA=1"     | SELECT "O" FOR SLAVE AND "1" FOR MASTER                                                                                    |

| 9  | "EXT START EDGE" "DATA =1"     | SELECT "1" FOR "POS" OR "O" FOR "NEG" CLOCK EDGE                                                                           |

| 10 | "EXT CLOCK EDGE" "DATA=1"      | SELECT "1" FOR "POS" OR "O" FOR NEG CLOCK EDGE                                                                             |

| 11 | "STOP-COIN START" "DATA=1"     | SELECT "1" FOR STOP* OR "O" FOR COIN* START                                                                                |

| 12 | "SIM HOLD CAM ENB" "DATA=O"    | "1" OR "YES" WILL ENABLE<br>SIM HOLD CAM BIT                                                                               |

| 13 | "CAM RESTART EDGE" "DATA=1"    | SELECT "1" FOR "POS" OR "O" FOR "NEG" CAM RESTART EDGE                                                                     |

| 14 | "DIAGNOSTICS" "DATA =0"        | SELECT DIAG. CAM MODE  1=REPLACE OUTPUT DATA WITH 16 BIT COUNTER  2=READ MICROPROCESSOR MEMORY  3=READ MICROPROCESSOR PORT |

- B.DA.6.(n)EF.CB.. Pressing the "CLR BACK" key after the B.DA.6.(n)EF key sequence will decrement the value of (n) for each pressing of the "CLR BACK" key.

- B.DA.6.(n)EF..DA Pressing the "DATA" key will cause the cursor to appear.

- B.DA.6.(n)EF.DA.nn Pressing keys from "0" to "9"

will enter the desired data.

- B.DA.6.(n)EF.DA.n.CB Pressing the "CLR BACK"

key will cancel the entry without changing

the format.

- B.DA.6.(n)EF.DA.n.EF Pressing the "ENTR FWD" key will enter the new resolution into the system.

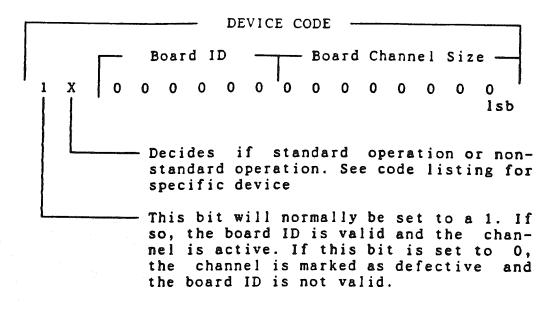

- B.DA.7.(n)EF Pressing the B.DA.7 key sequence followed by (n) pressings of the "ENTR FWD" key will display and permit editing and entering the list of boards in the system together with their listen and talk addresses. The first line of the display will read "BD ddd TYPE hhhh", where "ddd" is the decimal position of the entry, in the list beginning with zero, and is equal to (n)-1, and "hhhh" is the type of board in hexadecimal notation. The second line of the display will read "LADD lll TADD ttt", where "lll" is the listen address in hex and "ttt" is the talk address in hex.

- B.DA.7.(n)EF.CB.. Pressing the "CLR BACK" key after the B.DA.7.(n)EF key sequence will decrement the value of (n) for each pressing of the "CLR BACK" key.

- B.DA.7.(n)EF.DA Pressing the "DATA" key will cause the cursor to appear instead of "hhhh", the board type.

- B.DA.7.(n)EF.DA.n.. Pressing keys from "0" to "F"

will enter the type code for board number

"ddd".

- B.DA.7.(n)EF.DA.n..CB Pressing the "CLR BACK" key will cancel the entry without changing the board type. The cursor will replace the listen address, "lll".

- B.DA.7.(n)EF.DA.n..EF Pressing the "ENTR FWD"

key will enter the new board type. The

cursor will replace the listen address,

"111".

- B.DA.7.(n)EF.DA.n..EF.n.. Pressing keys from "0" to "F" will enter the listen address of the board "ddd".

- B.DA.7.(n)EF.DA.n..EF.n..CB Pressing the "CLR BACK" key will cancel the entry without changing the listen address. The cursor will replace the talk address, "ttt".

13

- B.DA.7.(n)EF.DA.n..EF.n..EF Pressing the "ENTR FWD" key will enter the new listen address. The cursor will replace the talk address, "ttt".

- B.DA.7.(n)EF.DA.n..EF.n..EF.n.. Pressing keys from "0" to "F" will enter the talk address for board number "ddd".

- B.DA.7.(n)EF.DA.n..EF.n..EB

Pressing the "CLR BACK" key will

cancel the entry without changing

the board type. The cursor

disappear.

- B.DA.7.(n)EF.DA.n..EF.n..EF.

Pressing the "ENTR FWD" key will enter the talk address. The cursor will disappear.

- B.DA.8.(n)EF Pressing the B.DA.8 key sequence followed by (n) pressings of the "ENTR FWD" key will display and permit editing and entering the list of input boards that have been removed from the system. entering the multiplexer address and the number of channels on the board, space will be saved in the channel sequence for the removed board. This removes the requirement for the user to reconfigure the host computer for the channel locations of the removed board. When this key sequence is pressed the first line of the display will read "REMOVED BOARD" and the second line of the display will read "FCH=ffff LGT=11", where "ffff" is the decimal number of the first channel on the board. "11" is the number of channels on the board in decimal notation. If (n) is one, then the board with the lowest first channel will be displayed. As (n) increases, the display will step through the list in the order of increasing first channel number.

- B.DA.8.(n)EF.CB.. Pressing the "CLR BACK" key after the B.DA.8.(n)EF key sequence will decrement the value of (n) for each pressing of the "CLR BACK" key.

- B.DA.8.(n)EF.DA Pressing the "DATA" key will cause the data in the second line of the display to disappear and the cursor to appear in place of the first channel number "ffff".

- B.DA.8.(n)EF.DA.n.. Pressing keys from "0" to "F" will enter the first channel number of the

board, "ffff".

- B.DA.8.(n)EF.DA.n..CB Pressing the "CLR BACK" key will cancel the entry without changing the first address. The cursor will appear in place of the length, "ll".

- <u>B.DA.8.(n)EF.DA.n..EF</u> Pressing the "ENTR FWD" key will enter the new first address and the cursor will replace the length, "ll".

- B.DA.8.(n)EF.DA.n..EF.n.. Pressing keys from

"O" to "F" will enter the length of the

board "ll".

- B.DA.8.(n)EF.DA.n..EF.n..CB Pressing the "CLR BACK" key will cancel the entry without changing board length, "ll".

- B.DA.8.(n)EF.DA.n..EF.n..EF Pressing the "ENTR FWD" key will enter the new board length, "ll". If the board length is zero then the board will not be entered into the list. If the first channel number is an existing entry in the list then a length of 0 will cause the entry to be deleted from the list.

- B.EF Pressing the key sequence B.EF is the same as press-ing the key sequence B.1.EF.

#### C The "RUN" key.

The "RUN" key will place the system into a run condition if it is in the "LOCAL" Mode. In both the "LOCAL" and "REMOTE" Modes, if the system is running, as indicated by the "RUN" LED being illuminated but not flashing, then the data for a selected channel will be displayed.

Pressing the "RUN" (C) key will cause the first line of the display to read "CHAN = nnnn " where "nnnn" is the decimal value of the channel that was previously read, or a channel within the first channel to last channel range. The second line of the display will read "SIGNAL = ". If the system is running then after channel "nnnn" has been digitized the second line of the display will read "SIGNAL = dddd " where "dddd" is the data for that channel displayed in the format selected using the "ENVR" key.

C.CB Pressing the "CLR BACK" key will cause the channel display to decrement. If the First Channel had been displayed then the display will wrap around to the Last Channel. When the displayed channel is digitized, the data for that channel will be displayed.

- C.DA Pressing the "DATA" key will cause the cursor to appear in place of the channel number.

- C.DA.nnnn Pressing keys "0" through "9" will enter desired channel number in decimal format.

- <u>C.DA.nnnn.CB</u> Pressing the "CLR BACK" key will delete the entered channel number and return to the previous channel number.

- C.DA.nnnn.EF Pressing the "ENTR FWD" key will enter the new channel number and after that channel has been digitized its data will be displayed.

- Pressing the "ENTR FWD" key will cause the channel display to increment. If the Last Channel had been displayed then the display will wrap around to the First Channel. When the displayed channel is digitized, the data for that channel will be displayed.

#### The "STOP" key.

The "STOP" key will stop a running system if it is in a local mode and turn off the "RUN" LED. Pressing the "STOP" (D) key will stop the system and cause the first line of the display to read "SYSTEM STOPPED" if the system is in the local control If the system is in the remote mode the first line of the display will read "SYSTEM STOPPED" or "SYSTEM RUNNING" as required.

#### E The "RST" key.

The "RST" key will reset the system variables. Pressing the "RST" (E) key will cause the first line of the display to read "TO RESET SYSTEM". The second line of the display will read "PRESS ENTR/FWD".

- Pressing the "ENTR FWD" key will cause the system to reset and clear the display.

- NOTE: If the "RST" key is held depressed while the AC system power is being turned on, a MASTER RESET will occur that will set the system defaults to a very slow generic operating mode.

#### F The "AUX" key.

The "AUX" key is a spare key reserved for special use and is not implemented in this system.

#### CB The "CLR BACK" key. The key code is 18.

The "CLR BACK" key has two uses depending on what Control Panel Function is being used. When the "ENTR FWD" key is used to step forward through a list of items, the "CLR BACK" key may be used as a backspace key to step backwards through the list. When data or addresses are being entered, if "CLR BACK" is pressed instead of the "ENTR FWD" key then the entered data will be cleared and no new information will be recorded.

#### <u>DA</u> The "DATA" key. The key code is 16.

The "DATA" key has two functions, for those Control Panel Functions that allow both mode control and data entry, pressing the "DATA" key will switch to the data display mode. For those Control Panel Functions that are already in the data display mode or have been switched to the data display mode, pressing the "DATA" key will cause the cursor to appear to allow data to be entered.

#### <u>EF</u> <u>The "ENTR FWD" key.</u> The key code is 19.

The "ENTR FWD" key has two uses depending on what Control Panel Function is being used. The "ENTR FWD" key can be used to step forward through a list of items, this use is normally prompted by the "PRESS ENTR/FWD" display. When data or addresses are being entered, pressing the "ENTR FWD" key will cause the new information to be recorded.

#### FN The "FNCT" key. The key code is 17.

The "FNCT" key is used to return the control entry to the "FUNCTION" or first level. At this level, the white notation on keys "0" through "F" is in effect and pressing one of those keys will enter the noted function. Since some functions automatically return to the "FUNCTION" level upon completion and other functions do not, it is suggested that every key stroke sequence commence with pressing the "FNCT" key until the user is familiar with the system. In the event that an incorrect sequence of key strokes are entered, the user can always return to the "FUNCTION" level by pressing the "FNCT" key.

#### REPORTED ERRORS CODES

- ERROR 2 Fatal, status read from TTL card not correct. Possible supply problem in the ADC block or Opto communication problem.

- ERROR 3 Fatal, setup not completed. Missing Opto/Interface or MC board.

- ERROR 4 Fatal, setup not completed. Not receiving response from Opto/Interface board.

- ERROR 5 Warning, Remote BCRC not matching hardware. Only Reported on powerup. (CCLK)

- ERROR 6 Fatal, Resolution not matching hardware. Correct jumpers on TTL card to match hardware. (BITS)

- ERROR 7 Data type or offset not matching hardware. Correct jumpers on TTL card to match hardware or Correct environment table to match jumpers on TTL card.

- ERROR 8 Full Scale not matching hardware. Correct jumpers on TTL card to match hardware or correct environment table to match jumpers.

- ERROR 9 Fatal, wrong TTL OUTPUT card, mode not supported.

Install TTL card for the ADC type being used.

- ERROR 10 Fatal, not defined operating mode, TTL card jumpers ?

- ERROR 11 Fatal, Bad Crystal Freq choosen. Correct environment table.

- ERROR 12 Warning, Remote PRE-CLOCK not equal to 1. Only reported on powerup. (SNCKRE)

- ERROR 13 Scan length is greater than 30K MAXIMUM LIMIT, or First > last channel. (Removed on 9989-02).

- ERROR 14 Coin for counter #1 is negative. First > last channel. (Removed on 9989-02).

- ERROR 15 Coin for counter #2 is negative. First > last channel. (Removed on 9989-02).

- ERROR 16 Coin for counter #3 is negative. First > last channel. (Removed on 9989-02).

- ERROR 17 Coin for counter #4 is negative. First > last channel. (Removed on 9989-02).

- ERROR 18 Crystal frequency is illegal in the Environment. Legal values are: 10Mhz, 5Mhz, 4Mhz, and 1Mhz. (20Mhz and 2Mhz legal on 9989-03).

- ERROR 19 Pre-Mux divisor too large for crystal used.

- ERROR 20 Pre-Burst divisor too large for crystal used.

- ERROR 21 CAM write scan length is greater than 30K, or first > last channel. (Removed on 9989-02).

- ERROR 22 Poll\* stuck Hi. (No channels recorded in config)

- ERROR 23 Poll\* stuck Lo.

- ERROR 24 Bus talk to system area, not allowed.

- ERROR 25 ADC timing not consistent with ADC type identified.

- ERROR 26 ADC block Mux Delay circuit not working.

- ERROR 27 Yanker card not responding or not installed if diagnostic mode 19 invoked.

- ERROR 27 ID/SIZE array overflow. Over 272 cards identified. This error reported if diagnostic mode 19 is NOT invoked.

- ERROR 28 Fatal, prom dash mismatch.

- ERROR 29 An attempt was made to adjust a digital TC pot, consult the factory if such an adjustment is required.

ERRORS 30-127 NOT DEFINED.

- ERROR 128 (CPU) SRESET1\* HI. (will not go LO).

- ERROR 129 (CPU) SRESET1\* F/F WILL NOT REMEMBER LO.

- ERROR 130 ERR128 AND ERR129

- ERROR 131 (CPU) SRESET1\* LO. (will not go HI).

- ERROR 132 ERR128 AND ERR131

- ERROR 133 ERR129 AND ERR131

- ERROR 134 ERR130 AND ERR131

- ERROR 135 (CPU) RESET2\* STUCK LO.

- ERROR 136 (CPU) RESET2\* STUCK HI.

- ERROR 137 ERR135 AND ERR136

- ERROR 138 (CPU) RESET3\* STUCK LO.

- ERROR 139 (CPU) RESET3\* STUCK HI.

- ERROR 140 ERR138 AND ERR139

- ERROR 141 (FIDIA) OVERRUN\* NOT WORKING. (FIFO-TO-CPU)

- ERROR 142 (FIDIA) FIFO SIZE ERROR (FIFO NOT 128K, 256K, 512K, OR 1MEG).

- ERROR 143 (FIDIA) READ TIME OUT FROM FIFO.

- ERROR 144 (CPU) CLRMXPRSNT\* DID NOT CLEAR MUX PRESENT F/F.

- ERROR 145 (CPU) MUX CLOCK DID NOT SET MUX PRESENT F/F.

- ERROR 146 ERR144 AND ERR145

- ERROR 147 (FIDIA) COMPARISON ERROR BETWWEEN FIFO DATA & CPU.

- ERROR 148 (CPU) STOP\* HI. (will not go LO).

- ERROR 149 (CPU) STOP\* LO. (will not go HI).

- ERROR 150 ERR148 AND ERR149

- ERROR 151 (FIDIA) CANNOT CLEAR DECOM F/F (FIFO ALWAYS TALKING?)

- ERROR 152 (CPU) STMORE is HI. (will not go LO).

- ERROR 153 (CPU) STMORE is LO. (will not go HI).

- ERROR 154 ERR152 AND ERR153

- ERROR 156 (CPU) DECOM is HI. (will not go LO).

- ERROR 157 (CPU) STMORE is HI. (will not go LO).

- ERROR 158 (CPU) ERROR READING INT5.5. (will not go LO).

- ERROR 159 (CPU) CANNOT SET DECOM. (will not go HI).

- ERROR 160 (CPU) INT5.5 is LO. (will not go HI).

- ERROR 161 (MC) MC CAM TEST FAILED COUNT TEST.

- ERROR 162 (MC) MC CAM TEST FAILED 5's TEST.

- ERROR 163 (MC) MC CAM TEST FAILED A'S TEST.

- ERROR 164 COMPARE ERROR --- LSB BYTE OF ADC TO OPTO TO BUS

- ERROR 165 COMPARE ERROR --- MSB BYTE OF ADC TO OPTO TO BUS

ERROR 166 MC CARD NOT INSTALLED OR BROKEN

ERROR 167 COMPARE ERROR WITH MC CARD ADD LINES

ERROR 168 FIFO NOT RESPONDING

#### INTRODUCTION.

This system is interfaced using the IEEE-488 interface protocol and therefore has special considerations regarding the system control and operation. This section of the manual details these considerations.

The basic programming steps indicated herein are compatible with the MCLS controlled systems now in use.

The IEEE-488 Bus structure as implemented by Preston follows the rules set by the IEEE-488 handbook. The Preston IEEE-488 Bus interface board uses a Fairchild 96LS488 controller chip to interpret the IEEE-488 bus signals and transmit data to and from a PRESYS 1000 Controller.

The Controller transmits and receives 16-bit words which are broken into bytes by the 96LS488 for bus transmission. The interface will respond to any IEEE-488 bus command. The most commonly used commands are: SERIAL POLL (Status), WRITE (data to PRESYS), READ (data from PRESYS), and CLEAR (initialize interface).

The signals TRANSMIT TERMINATE and READ TERMINATE must be disabled, as READ TERMINATE is not generated by the PRESYS bus, and TRANSMIT TERMINATE causes false data to be transmitted to the PRESYS controller.

#### 4.0 PROGRAMMING

Programming the PRESYS 1000 through the IEEE-488 Bus:

- 1. Before attempting to transmit data to the PRESYS 1000 system, a Device Clear <u>MUST</u> be sent to the PRESYS 1000 system address, in order to set the byte steering logic in the proper direction for data transmission.

- 2. It should be noted that most computers send and receive data in reverse order from Hewlett-Packard computers. This is true, for example, for Digital Equipment Corporation computers. The sequence in which the bytes are sent can be reversed by changing straps on the IEEE-488 Control board, part number 201060.

This eliminates the need to reverse the sequence of bytes through software in the computer. The standard factory settings for the various dash number variations of the 201060 board are given in the following table:

IEEE-488 INTERFACE BOARD

P. C. ASSEMBLY PART NUMBER 201060

DASH NUMBER TABULATION

| DASH NO. | STRA      | AP       | NOTES |              |            |

|----------|-----------|----------|-------|--------------|------------|

| -00      | A-B, C-D, | E-F, G-H | SENDS | HIGHER-ORDER | BYTE FIRST |

| -01      | A-D. B-C. | E-H G-F  | SENDS | LOWER-ORDER  | BYTE FIRST |

#### 5.0 STATUS BITS

The status bits are defined in the following table:

#### STATUS BIT TABLE

| BIT NUMBER | BIT DEFINITIO | BIT DEFINITION        |  |  |  |  |

|------------|---------------|-----------------------|--|--|--|--|

| 1          | EMPTY*        | (Fifo status)         |  |  |  |  |

| 2          | OVERRUN*      | (Fifo status)         |  |  |  |  |

| 3          | FULL*         | (Fifo status)         |  |  |  |  |

| 4          | STOP*         | (Presys status)       |  |  |  |  |

| 5          | HALF FULL*    | (Fifo status)         |  |  |  |  |

| 6          | MISC.0        | (future use, tied HI) |  |  |  |  |

| 7          | ( )           | (IEEE for polling)    |  |  |  |  |

| 8          | ERROR*        | (CPU status)          |  |  |  |  |

#### REQUEST SERVICE (RSV) LINE

Installing jumper W10 will connect the IEEE request service (RSV) input line to the fifo OVERRUN\* signal. OVERRUN\* is asserted when ADC data tries to write to a full fifo. If RSV is to be used with some other status, say EMPTY\* for example, a wire-wrap wire must be used to complete the connection. See schematic 201061-T for connection possibilities.

#### 6.0 CONTROL WORD BIT 2.

Bit 2, handshake enable bit. This bit should be programmed true insuring the ability to always transmit data. If this bit is false TXRDY will be left false possibly inhibiting data transmission.

#### DIP SWITCH SETTINGS.

Setting the Device addresses