Enhanced Serial Highway Driver for SCSI

## INSTRUCTION MANUAL

July, 1994

(C) 1993, 1994 Copyright by KineticSystems Corporation Lockport, Illinois All rights reserved

## CONTENTS

| reatures and Applications          |     |

|------------------------------------|-----|

| General Description                |     |

| Function Codes                     |     |

| Ordering Information               | . Z |

| SCSI BUS                           | . 3 |

| SCSI BUS SIGNALS                   | . 3 |

| SCSI SIGNAL SOURCES                | 4   |

| SCSI BUS TIMING                    | . 5 |

| SCSI BUS PHASES                    | 7   |

| BUS FREE Phase                     |     |

| ARBITRATION Phase                  |     |

| SELECTION Phase                    |     |

| SELECTION Timeout Procedure        |     |

| RESELECTION Phase                  |     |

| RESELECTION Timeout Procedure      |     |

| Information Transfer Phases        | 10  |

| Asynchronous Information Transfers | 11  |

| Synchronous Information Transfers  | 12  |

| COMMAND Phase                      | 13  |

| MESSAGE Phase                      | 13  |

| MESSAGE IN Phase                   | 13  |

| MESSAGE OUT Phase                  | 14  |

| Signal Restriction Between Phases  | 14  |

| SCSI Bus Conditions                | 14  |

| ATTENTION Condition                | 14  |

|                                    | 15  |

| Reset Condition                    | 15  |

| naru neset Alternative             | 10  |

| SCSI BUS PHASE SEQUENCERS          | 16  |

| Message System Specification       |     |

| Message Codes                      | 17  |

| Message Codes                      | 11  |

| SCSI MESSAGES                      | 17  |

| COMMAND COMPLETE                   | 17  |

| DISCONNECT                         | 17  |

| INITIATOR DETECTED ERROR           | 18  |

| ABORT                              | 18  |

| MESSAGE REJECT                     | 18  |

| NO OPERATION                       | 18  |

| MESSAGE PARITY ERROR               | 18  |

| BUS DEVICE RESET                   | 19  |

|                                    |     |

| IDENTIFY                                       |      |

|------------------------------------------------|------|

| SCSI COMMAND SPECIFICATION                     |      |

|                                                |      |

| Command Descriptor Block                       |      |

| Logical Unit Number                            |      |

| Logical Unit Address                           |      |

| Transfer Length                                |      |

| Reserved                                       |      |

| Control Byte                                   |      |

| Completion Status Byte                         | . 23 |

| COMMANDS SUPPORTED BY THE 2145                 | . 25 |

| TEST UNIT READY Command                        | . 25 |

| REQUEST SENSE Command                          |      |

| Error/Status Register                          |      |

| Sense Keys and Codes                           |      |

| INQUIRY Command                                |      |

| SEND DIAGNOSTIC Command                        |      |

| SINGLE CAMAC OPERATION Command                 |      |

| BLOCK TRANSFER CAMAC OPERATION Command         |      |

|                                                |      |

| BOOK LAM Command                               | . 47 |

| UNBOOK LAM COMMAND                             | . 49 |

| REGISTER ACCESS COMMAND                        | . 50 |

| Timer Control/SCSI ID/Strap Selection Register |      |

| Timer Data                                     |      |

| Control/Status Register                        |      |

| Buffer Interval Counter                        |      |

| Buffer End Address/Counter #2                  |      |

|                                                |      |

| LED Register                                   |      |

| DMA Memory Address Register                    |      |

| Reset Interface                                |      |

| Buffer End Address                             |      |

| Reset CAMAC Write/Read FIFO                    |      |

| Reset Demand FIFO                              |      |

| Execute List                                   |      |

| Command Memory Data                            |      |

| CAMAC Word Count Register                      |      |

| Reset Buffer Address Register #1               | . 58 |

| Reset Buffer Address Register #2               |      |

| Command Memory Address Register                |      |

| Demand Message Register                        |      |

| LOAD LIST Command                              |      |

| EXECUTE LIST Command                           |      |

| RESUME LIST Command                            |      |

| STADE TIMES Command                            | . 61 |

| Timer Data                                           | 63  |

|------------------------------------------------------|-----|

| Buffer Interval Counter                              |     |

| Buffer Ending Address                                | 63  |

| Trigger Mode/Append Status                           | 63  |

| TIMER STATUS Command                                 | 65  |

| STOP TIMER Command                                   | 66  |

| READ BLOCK Command                                   | 67  |

| CAMAC Operating Modes                                | 68  |

| CAMAC NAF Specifications                             | 68  |

| Executing Single Transfer Operations                 | 69  |

| Executing Block Transfer Operations                  | 71  |

| Executing Block Transfer Operations                  | 72  |

| Block Transfer Mode Control                          | 12  |

| Conservative Block Transfer Operations               | 74  |

| Q-Stop Block Transfer Operations                     | 74  |

| Q-Ignore Block Transfer Operations                   | 74  |

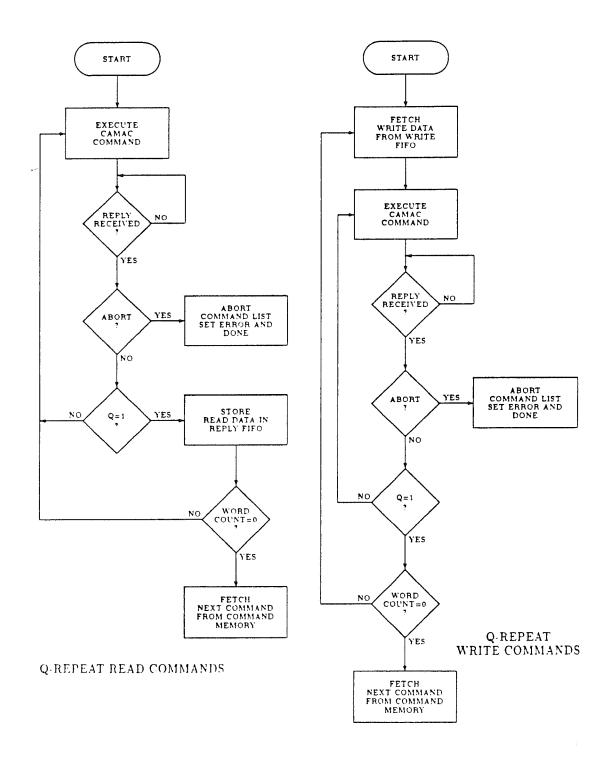

| Q-Repeat Block Transfer Operations                   | 75  |

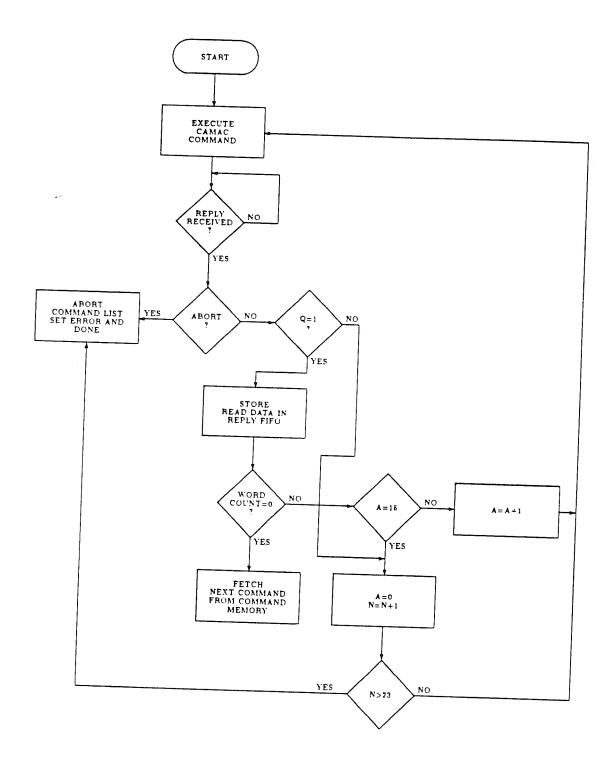

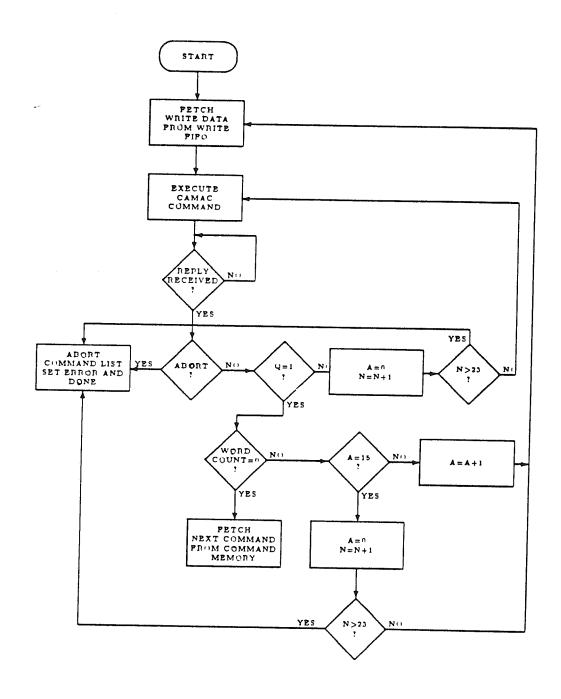

| Q-Scan Block Transfer Operations                     | 75  |

| Enhanced Block Transfer Operations                   | 80  |

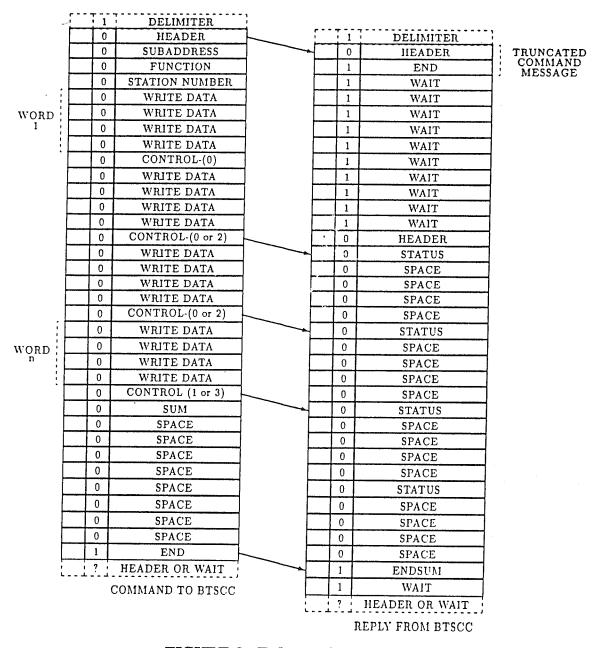

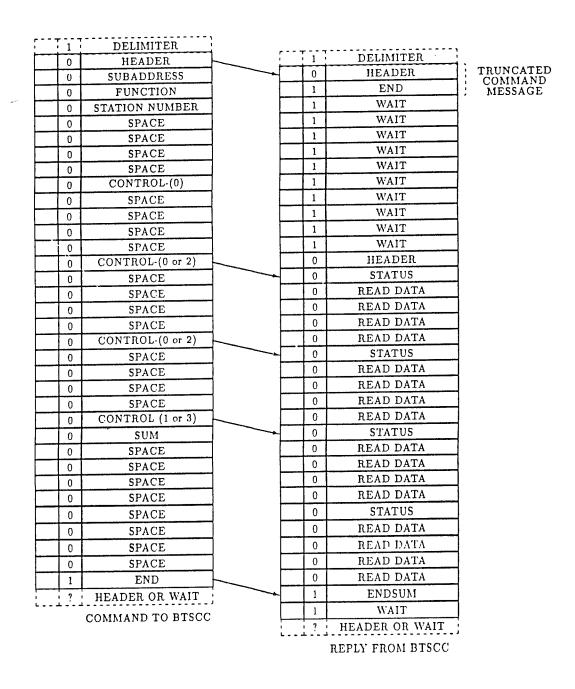

| Enhanced Serial Highway Command/Reply Sequence       | 80  |

| Single NAF Q-Stop Enhanced Block Transfer            |     |

| Single NAF Q-Ignore Enhanced Block Transfer          |     |

| Single NAF Q-Repeat Enhanced Block Transfer          | 83  |

| Enhanced Serial Highway List Sequencing              | 84  |

| Q-Repeat Enhanced Serial Highway List Sequencer Mode | 84  |

| Q-Ignore Enhanced Serial Highway List Sequencer Mode | 85  |

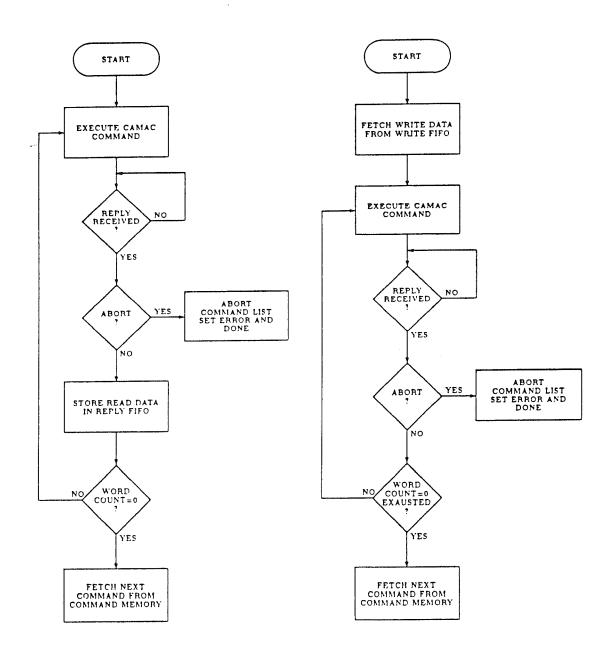

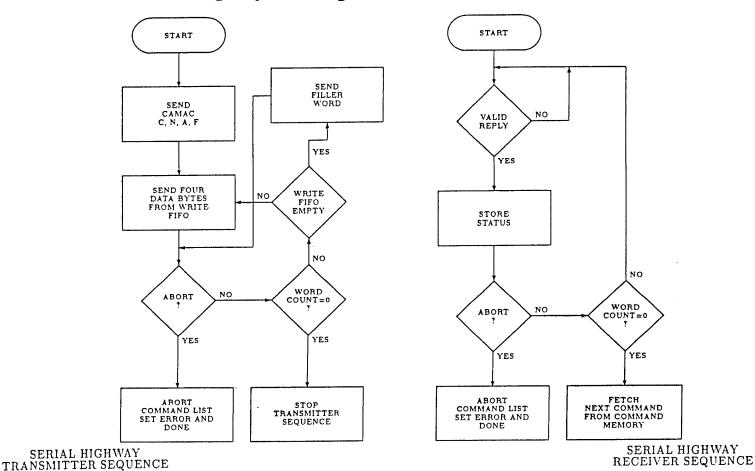

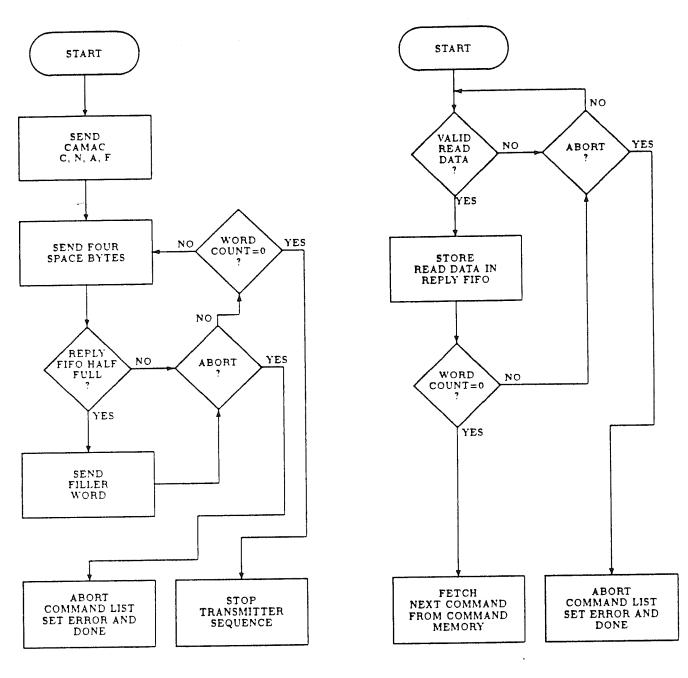

| Enhanced Serial Highway Flow Diagrams                | 85  |

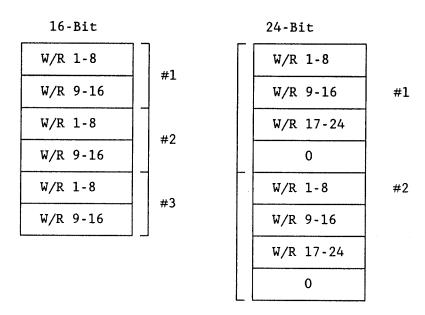

| Data Storage Format                                  | 87  |

| Asynchronous Event Notification                      | 87  |

| List Processing                                      | 88  |

| List Processing Format                               | 88  |

| Instruction Byte 1                                   | 89  |

| Instruction Byte 2                                   | 90  |

| Instruction Byte 3                                   | 90  |

| Instruction Byte 4                                   |     |

| Instruction Bytes 5 through 8                        | 91  |

| Single CAMAC Operation Instruction                   | 91  |

| Single Write With In-Line Data Instruction           | 92  |

| Conservative Block Transfer Instruction              | 92  |

| Enhanced Block Transfer Instruction                  | 93  |

| HALT Instruction                                     | 94  |

| List Processing Operation                            | 94  |

| List Processing Example                              | 95  |

| Timer Initiated List Execution                       | 96  |

| SCSI Connectors                                      | 98  |

| Soci confidences                                     | 50  |

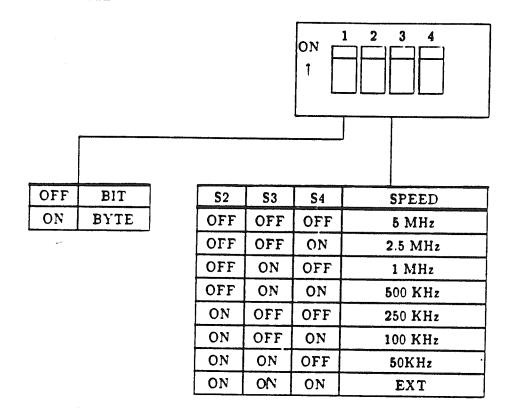

| SCSI Switch Selections                               | 100 |

| <del></del>                                          | 100 |

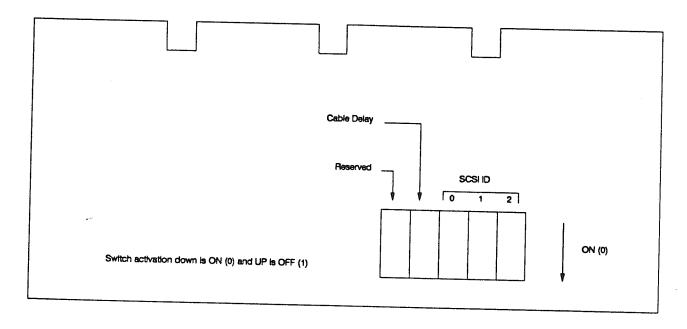

| Strap Options                                        |     |

| outap Ophions                                        | 102 |

| Demands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 103 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Unbypass and Loop Collapse Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Front Panel Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Front Panel Test Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| External Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

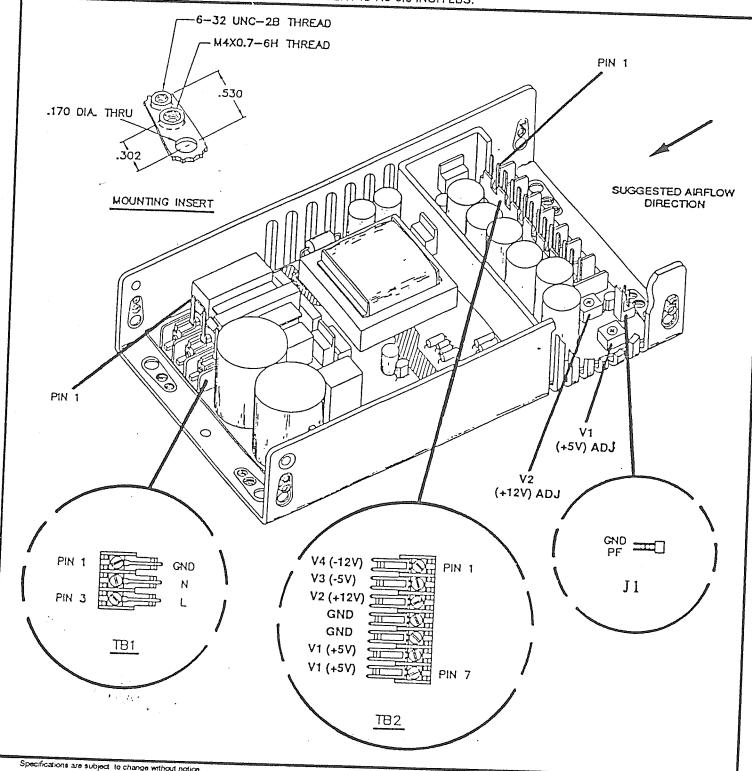

| Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

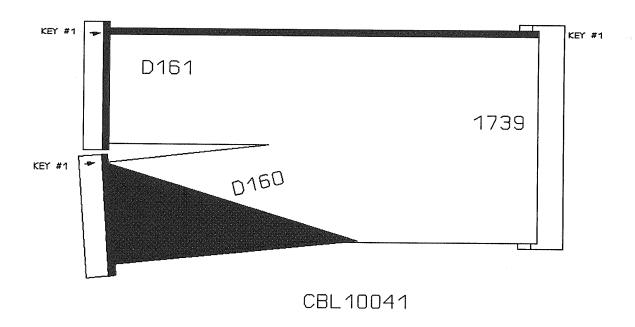

| 2145 Cable Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100 |

| TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| TABLE 1 - SCSI Signal Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5   |

| TABLE 2 - SCSI Transfer Phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| TABLE 3 - 2145 Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| TABLE 4 - First Byte in Command Description Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| TABLE 5 - Six Byte in Command Description Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22  |

| TABLE 6 - Command Description Block Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23  |

| TABLE 7 Status Buts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23  |

| TABLE 7 - Status Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24  |

| TABLE 9 - 2145 Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25  |

| TABLE 10 - Test Unit Ready Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25  |

| TABLE 11 - Request Sense Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26  |

| TABLE 12 - 14-Byte Request Sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27  |

| TABLE 13 - INQUIRY Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39  |

| TABLE 14 - 8-Byte INQUIRY Header Return                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40  |

| TABLE 15 - SEND DIAGNOSTIC Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44  |

| TABLE 16 - Single CAMAC Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45  |

| TABLE 17 - BLOCK Transfer CAMAC Operation Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46  |

| TABLE 18 - BOOK LAM Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48  |

| TABLE 19 - Command Descriptor Block for UNBOOK LAM Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49  |

| TABLE 20 - REGISTER ACCESS Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50  |

| TABLE 21 - LOAD LIST Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59  |

| TABLE 22 - EXECUTE LIST Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60  |

| TABLE 23 - RESUME LIST Command Descriptor Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61  |